| SPE  | FI | $C\Delta I$ | NS  |

|------|----|-------------|-----|

| OF L |    | $\Box$      | 110 |

CUSTOMER . MIE

SAMPLE CODE . SE12864WRF-004HC1Q

MASS PRODUCTION CODE . PE12864WRF-004HC1Q

SAMPLE VERSION . 01

SPECIFICATIONS EDITION . 002

DRAWING NO. (Ver.) · JLMD- PE12864WRF-004HC1Q\_001

PACKAGING NO. (Ver.) : JPKG- PE12864WRF-004HC1Q\_001

# **Customer Approved**

Date:

POWERTIP 2013.08.23 JS RD APPROVED

| Approved | Checked | Designer |

|----------|---------|----------|

|          | 劉進      | 李誠       |

| Ryan     | Lori    | Bruce    |

|          |         |          |

☐ Preliminary specification for design input

■ Specification for sample approval

## POWERTIP TECH. CORP.

**Headquarters:** No.8, 6<sup>th</sup> Road, Taichung Industrial Park,

Taichung, Taiwan

台中市 407 工業區六路 8號

TEL: 886-4-2355-8168

FAX: 886-4-2355-8166

E-mail: <a href="mailto:sales@powertip.com.tw">sales@powertip.com.tw</a>

Http://www.powertip.com.tw

# **History of Version**

| Date (mm / dd / yyyy) | Ver. | Edi. | Description          | Page | Design by |

|-----------------------|------|------|----------------------|------|-----------|

| 01/18/2006            | 0    | 0    | New Sample           | -    | 劉傳德       |

| 07/29/2013            | 01   | 001  | Change Stiffener     | -    | 李誠        |

| 08/23/2013            | 01   | 002  | Update Specification | -    | 李誠        |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

|                       |      |      |                      |      |           |

Total: 30Page

#### Contents

## 1. SPECIFICATIONS

- 1.1 Features

- 1.2 Mechanical Specifications

- 1.3 Absolute Maximum Ratings

- 1.4 DC Electrical Characteristics

- 1.5 Optical Characteristics

- 1.6 Backlight Characteristics

## 2. MODULE STRUCTURE

- 2.1 Counter Drawing

- 2.2 Interface Pin Description

- 2.2.1 Application Notes

- 2.2.2 Refer Initial code

- 2.3 Timing Characteristics

- 2.4 Power supply for LCD module

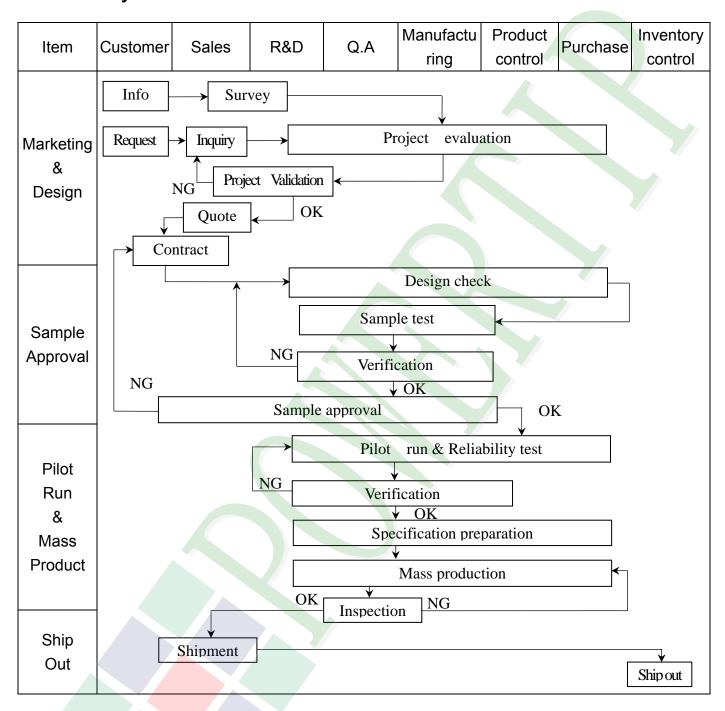

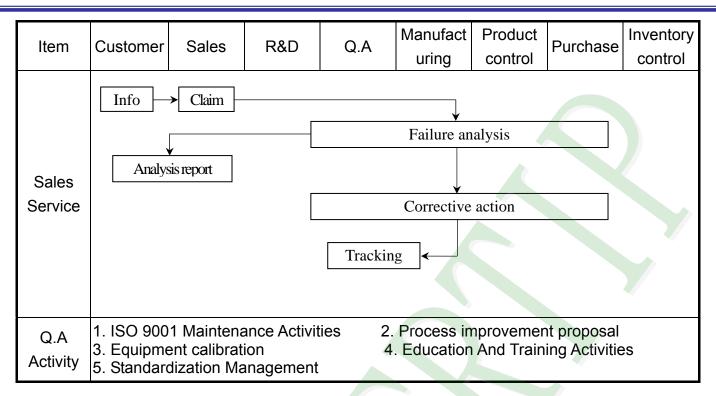

## 3. QUALITY ASSURANCE SYSTEM

- 3.1 Quality Assurance Flow Chart

- 3.2 Inspection Specification

### 4. RELIABILITY TEST

4.1 Reliability Test Condition

# 5. PRECAUTION RELATING PRODUCT HANDLING

- 5.1 Safety

- 5.2 Handling

- 5.3 Storage

- **5.4** Terms of Warranty

# **Appendix:**

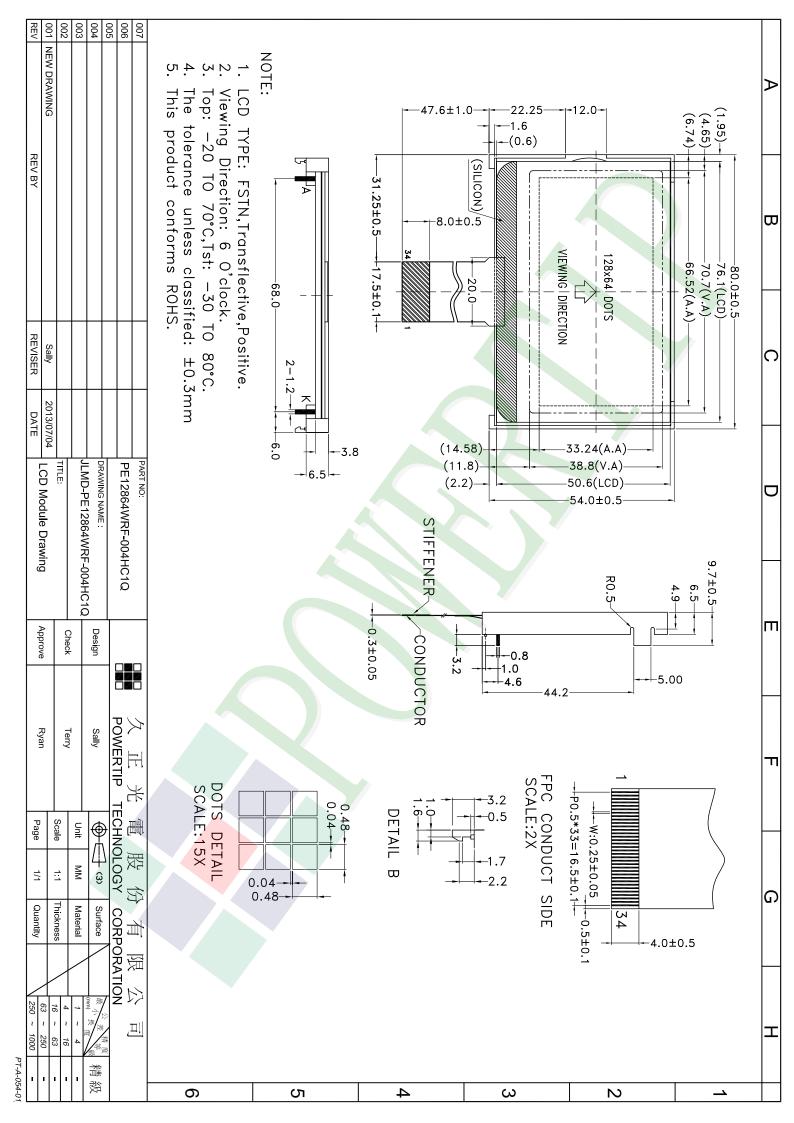

- 1.LCM drawing

- 2. Packaging Specification

Note: For detailed information please refer to IC data sheet: Sitronix -ST7565S-G

## 1. SPECIFICATIONS

## 1.1 Features

| Item                        | Standard Value                                               |

|-----------------------------|--------------------------------------------------------------|

| Display Type                | 128 * 64 Dots                                                |

| LCD Type                    | FSTN White , Positive , Transflective,Extended Temp          |

| Driver Condition            | LCD Module : 1/65 Duty , 1/9 Bias                            |

| Viewing Direction           | 6 O'clock                                                    |

| Backlight                   | White LED B/L                                                |

| Weight                      | 25g                                                          |

| Interface                   | 8-bit parallel data input and serial data input              |

| Other(controller/driver IC) | ST7565S-G                                                    |

|                             | THIS PRODUCT CONFORMS THE ROHS OF PTC                        |

| ROHS                        | Detail information please refer web site :                   |

|                             | http://www.powertip.com.tw/news.php?area_id_view=1085560481/ |

1.2 Mechanical Specifications

| Item              | Standard Value                   | Unit |

|-------------------|----------------------------------|------|

| Outline Dimension | 80.0 (L) * 54.0 (w) *10.3max (H) | mm   |

| Viewing Area      | 70.7 (L) *38.8 (w)               | mm   |

| Active Area       | 66.52 (L) * 33.24 (w)            | mm   |

| Dot Size          | 0.48 (L) * 0.48 (w)              | mm   |

| Dot Pitch         | 0.52 (L) * 0.52(w)               | mm   |

Note: For detailed information please refer to LCM drawing

1.3 Absolute Maximum Ratings

| Item                      | Symbol          | Condition | Min. | Max.    | Unit                 |

|---------------------------|-----------------|-----------|------|---------|----------------------|

| Power Supply Voltage      | $V_{dd}$        | _         | -0.3 | 5.0     | V                    |

| LCD Driver Supply Voltage | $V_{LCD}$       | _         | -18  | 0.3     | V                    |

| Input Voltage             | V <sub>IN</sub> | _         | -0.3 | VDD+0.3 | V                    |

| Operating Temperature     | T <sub>OP</sub> | _         | -20  | 70      | $^{\circ}\mathbb{C}$ |

| Storage Temperature       | T <sub>ST</sub> | _         | -30  | 80      | $^{\circ}\mathbb{C}$ |

| Storage Humidity          | H <sub>D</sub>  | Ta<60 ℃   | -    | 90      | %RH                  |

# 1.4 DC Electrical Characteristics

Ta = 25°℃

| Item                 | Symbol             | Condition              | Min.   | Тур. | Max.   | Unit |

|----------------------|--------------------|------------------------|--------|------|--------|------|

| Logic Supply Voltage | $V_{dd}$           | -                      | 3.0    | 3.3  | 3.6    | V    |

| "H" Input Voltage    | V <sub>IH</sub>    | -                      | 0.8VDD | _    | VDD    | V    |

| "L" Input Voltage    | V <sub>IL</sub>    | -                      | VSS    | -    | 0.2VDD | V    |

| "H" Output Voltage   | V <sub>OH</sub>    | -                      | 0.8VDD | ı    | VDD    | V    |

| "L" Output Voltage   | $V_{OL}$           |                        | VSS    | ı    | 0.2VDD | V    |

| Supply Current       | I <sub>dd</sub> *1 | V <sub>DD</sub> = 3.3V | -      | 0.2  | 1.0    | mA   |

| LCM Driver Voltage   | V <sub>OP</sub> *2 | <b>25</b> ℃            | 9.4    | 9.7  | 10     | V    |

NOTE: \*1 The Maximum current display

\*2 The VOP test point is VDD-V5

## 1.5 Optical Characteristics

LCD Panel:1/65Duty,1/9Bias,V<sub>LCD</sub> =9.7V,Ta =25°C

| Item                                   |            | Symbol | Conditions         | Min. | Тур. | Max. | Unit              | Reference |

|----------------------------------------|------------|--------|--------------------|------|------|------|-------------------|-----------|

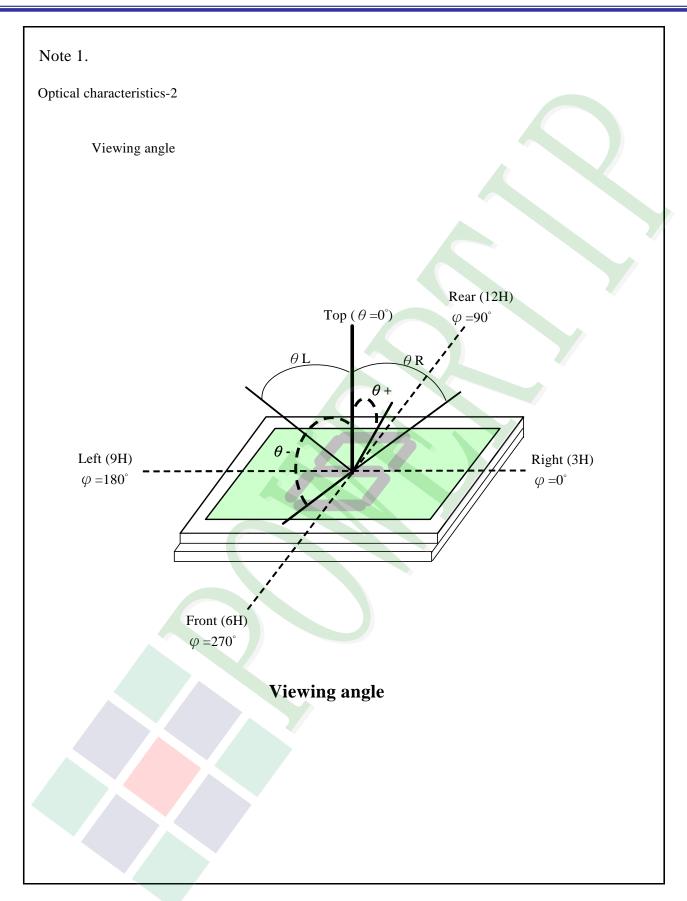

| Response Time                          | Rise       | tr     | _                  | -    | 150  | 300  | ms                | Notes 2   |

| response fille                         | Fall       | tf     | _                  | -    | 150  | 300  | ПЗ                | 140163 2  |

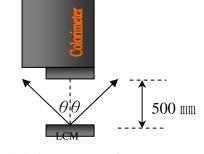

|                                        | Тор        | Θ+     |                    | 1    | 40   | -    |                   |           |

| Viewing angle                          | Bottom     | Θ-     | C <u>&gt;</u> 2.0, | 1    | 40   | -    | Deg.              | Notes 1   |

| range                                  | Left       | ΘL     | 0 <u>~</u> 2.0,    | -    | 45   | -    | Deg.              | INOTES I  |

|                                        | Right      | ΘR     |                    | -    | 45   | -    |                   |           |

| Contrast Ratio (With LCD, Without B/L) |            | CR     | θ = 0°             | -    | 5    | -    |                   | Note 3    |

| CIE Color Coor                         | dinate     | Х      |                    | 0.27 | 0.32 | 0.37 |                   | Notes 4   |

| (With LCD)                             |            | Y      | IF=30 mA           | 0.30 | 0.35 | 0.40 |                   | Notes 4   |

| Average Brightness (with LCD) *1       |            | IV     | 11 -30 IIIA        | 50   | 70   | -    | cd/m <sup>2</sup> |           |

| Uniformity '                           | <b>`</b> 2 | ∆B     |                    | 70   | -    | -    | %                 | Notes 4   |

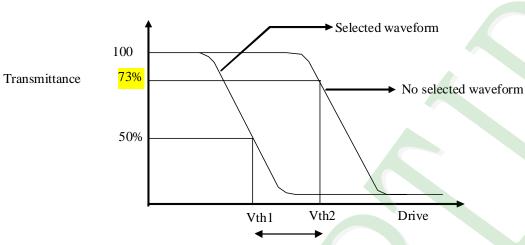

### Note 4

- 1 : △B=B(min) / B(max) \* 100%

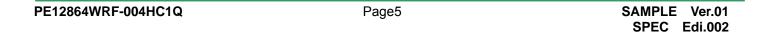

- 2 : Measurement Condition for Optical Characteristics:

- a : Environment: 25°C±5°C / 60±20%R.H → no wind → dark room below 10 Lux at typical lamp current and typical operating frequency.

- b : Measurement Distance:  $500 \pm 50 \text{ mm}$  ,  $(\theta = 0^{\circ})$

- c: Equipment: TOPCON BM-7 fast, (field 1°), after 10 minutes operation.

- d: The uncertainty of the C.I.E coordinate measurement ±0.01, Average Brightness ± 4%

Colorimeter=BM-7 fast

#### Electrical characteristics-2

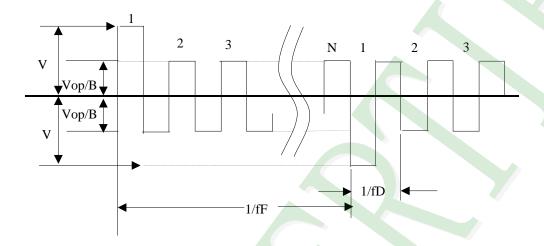

<sup>™</sup> 2 Drive waveform

Vop: Drive voltage fF: Frame frequency 1/B: Bias fD: Drive frequency

N: Duty

#### (1) Selected waveform

#### (2) Non- Selected wave form

#### Note:

Frame frequency is defined as follows: Common side supply voltage peak - to - peak /2 = 1 period

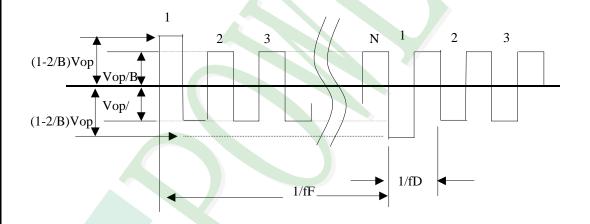

Note 3.: Definition of Vth

Active voltage range

|                | Vth1                | Vth2                   |

|----------------|---------------------|------------------------|

| View direction | 10 °                | 40 °                   |

| Drive waveform | (Selected waveform) | (No selected waveform) |

| Transmittance  | 50%                 | 73%                    |

**※**1 Contrast ratio

= (Brightness in OFF state) / (Brightness in ON state)

Outline of Electro-Optical Characteristics Measuring System

# 1.6 Backlight Characteristics

LED Backlight

**Maximum Ratings**

| Item              | Symbol | Conditions | Min. | Max.  | Unit |

|-------------------|--------|------------|------|-------|------|

| Forward Current   | IF     | Ta =25°ℂ   | -    | 240   | mA   |

| Reverse Voltage   | VR     | Ta =25°ℂ   | - 🔥  | 10.4  | V    |

| Power Dissipation | PD     | Ta =25°ℂ   | - ^  | 1.248 | W    |

**Electrical / Optical Characteristics**

| Item                             | Symbol | Conditions | Min.  | Тур. | Max. | Unit              |

|----------------------------------|--------|------------|-------|------|------|-------------------|

| Forward Voltage                  | VF     |            |       | 5.0  | 5.2  | V                 |

| Average Brightness (without LCD) | IV     | IF=160 mA  | 300   | 370  | -    | cd/m <sup>2</sup> |

| CIE Color Coordinate             | X      |            | 0.255 | 1    | 0.34 |                   |

| (Without LCD)                    | Y      |            | 0.265 | -    | 0.35 | 1                 |

| Color                            |        |            | White |      |      |                   |

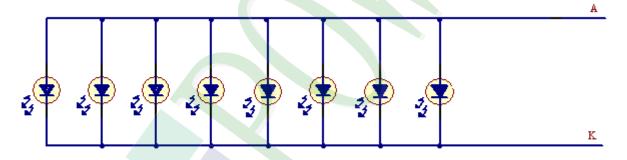

# Internal Circuit Diagram:

## 2. MODULE STRUCTURE

# 2.1 Counter Drawing

## 2.1.1 LCM Mechanical Diagram

\* See Appendix

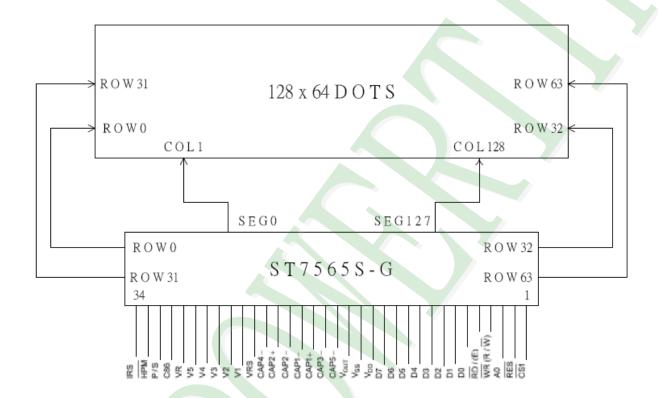

## 2.1.2 Block Diagram

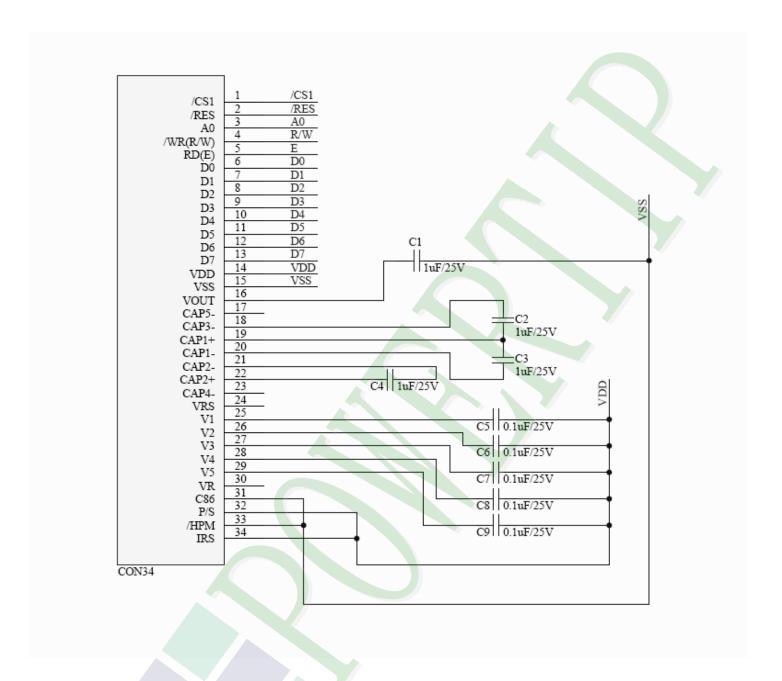

# 2.2 Interface Pin Description

| Pin No. | Symbol | Function                                                                                                     |

|---------|--------|--------------------------------------------------------------------------------------------------------------|

|         | 1004   | This is the chip select single. When /CS1= L and /CS2 = H then the                                           |

| 1       | /CS1   | chip select becomes active, and data/command I/O is enabled.                                                 |

| 2       | /DEC   | When /RES is set to L the settings are initialized.                                                          |

| 2       | /RES   | The reset operation is perform by the /RES single level.                                                     |

|         |        | This is connected to the least significant bit of the normal MPU address                                     |

| 3       | A0     | bus, and it determines whether the data bits are data or a command.                                          |

|         | 710    | A0 = H : Indicates that D0 to D7 are display data.                                                           |

|         |        | A0 = L : Indicates that D0 to D7 are control data.                                                           |

|         |        | When connected to an 8080 MPU, this is active LOW.                                                           |

|         |        | (R/W) This terminal connects to the 8080 MPU WR single. The                                                  |

|         |        | signals on the data bus are latched at the rising edge of                                                    |

| 4       | /WR    | the WR signal.                                                                                               |

| '       | (R/W)  | When connected to a 6800 Series MPU:                                                                         |

|         |        | This is the read/write control signal input terminal.                                                        |

|         |        | When R/W = H : Read.                                                                                         |

|         |        | When R/W = L : Write.                                                                                        |

|         |        | When connected to an 8080 MPU, this is active LOW.                                                           |

|         | /RD    | (E) This pin is connected to the RD signal of the 8080 MPU, and the                                          |

| 5       | (E)    | ST7565S series data bus is in an output status when this signal is L .                                       |

|         | (-/    | When connected to an 8080 MPU, this is active HIGH.                                                          |

|         |        | This is the 6800 Series MPU enable clock input terminal.                                                     |

| 6       | D0     |                                                                                                              |

| 7       | D1     | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16 bit                                 |

| 8       | D2     | standard MPU data bus.                                                                                       |

| 9       | D3     | When the serial interface is selected ( P/S = L ):                                                           |

| 10      | D4     | D7 : serial data input (SI) ; D6 : the serial clock input (SCL)                                              |

| 11      | D5     | D0 to D5 are set to high impedance.  When the chip select is not active, D0 to D7 are set to high impedance. |

| 12      | D6     | their the employees to her detive, be to by die eet to high impedance.                                       |

|         |        |                                                                                                              |

| 13      | D7     |                                                                                                              |

| 14      | VDD    | Shared with the MPU power supply terminal VCC.                                                               |

| 15      | VSS    | This is a 0V terminal connected to the system GND.                                                           |

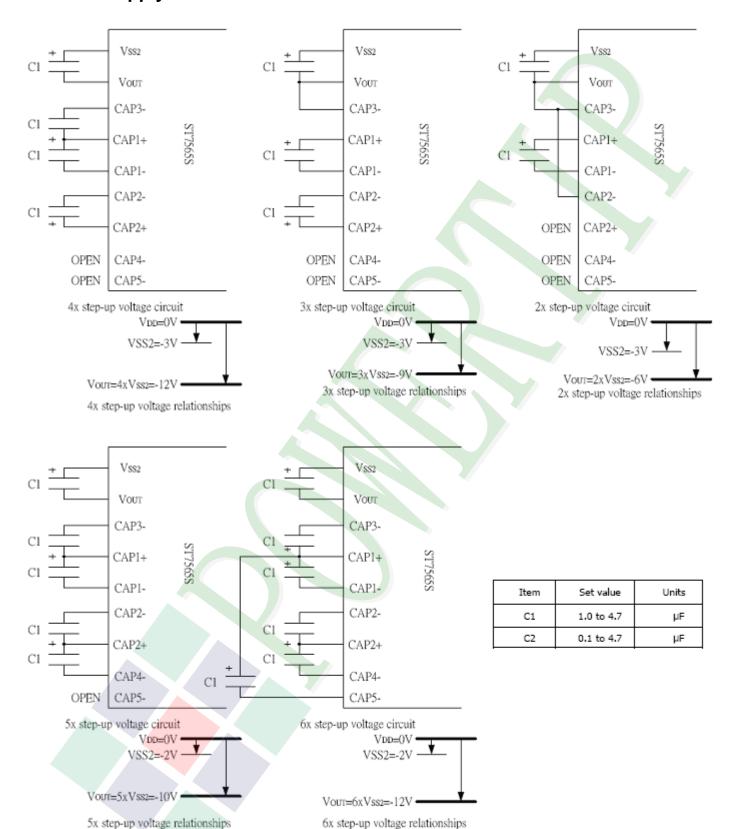

| 16      | VOUT   | DC/DC voltage converter. Connect a capacitor between this terminal and VSS.                                  |

| Pin No. | Symbol | Function                                                                                                                                                                                                                                                        |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | CAP5-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                      |

| 18      | CAP3-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                      |

| 19      | CAP1+  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.                                                                                                                                                                      |

| 20      | CAP1-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                      |

| 21      | CAP2-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                      |

| 22      | CAP2+  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2- terminal.                                                                                                                                                                      |

| 23      | CAP4-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                      |

| 24      | VRS    | This is the internal-output VREG power supply for the LCD power supply voltage regulator.                                                                                                                                                                       |

| 25      | V1     |                                                                                                                                                                                                                                                                 |

| 26      | V2     | This is a multi-level power supply for the liquid crystal drive. The voltage                                                                                                                                                                                    |

| 27      | V3     | Supply applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the                                                                                                                  |

| 28      | V4     | impedance using an op.amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.                                                                                                                                   |

| 29      | V5     |                                                                                                                                                                                                                                                                 |

| 30      | VR     | Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divider.  IRS = L : the V5 voltage regulator internal resistors are not used.  IRS = H : the V5 voltage regulator internal resistors are used.           |

| 31      | C86    | This is the MPU interface switch terminal.  C86 = H : 6800 Series MPU interface.  C86 = L : 8080 MPU interface.                                                                                                                                                 |

| 32      | P/S    | This is the parallel data input/serial data input switch terminal.  P/S = H : Parallel data input.  P/S = L : Serial data input.                                                                                                                                |

| 33      | /HPM   | This is the power control terminal for the power supply circuit for liquid crystal drive.  HPM = H : Normal mode.  HPM = L : High power mode.                                                                                                                   |

| 34      | IRS    | This terminal selects the resistors for the V5 voltage level adjustment. IRS = H : Use the internal resistors. IRS = L : Do not use the internal resistors. The V5 voltage level is regulated by external resistive voltage divider attached to the VR terminal |

## 2.2.1 Application Notes:

#### `2.2.2 Refer Initial code:

```

void Initial Main(void)

{

WriteCOM Main(0xE2);

//Reset Function

WriteCOM_Main(0x2F);

// Power controller set

WriteCOM Main(0xA2);

//SET LCD BIAS=1/9 ,BS=0=1/9 BS=1=1/7

WriteCOM Main(0x26);

//V5 voltage regulator internal resistor ratio set

// SET 6.0

WriteCOM Main(0x81);

//SET REFERENCE VOLTAGE

WriteCOM Main(0x24);

(1+ra/rb)*(1-\alpha/162)VREG=9.8V

// 24=36

WriteCOM_Main(0xC0);

//Commom output mode

WriteCOM Main(0xA1);

// ADC Select 0xa1

WriteCOM Main(0xA6);

//Display normal

WriteCOM Main(0x40);

//Display start line

WriteCOM Main(0xF8);

//Booster set

WriteCOM Main(0x00);

// 0:4X 1:5X

WriteCOM_Main(0xA4);

// Display All Points ON/OFF

// 0:Normal display mode

// 1:Display all points ON

//-----Display On-

WriteCOM_Main(0xAF);

```

## 2.3 Timing Characteristics

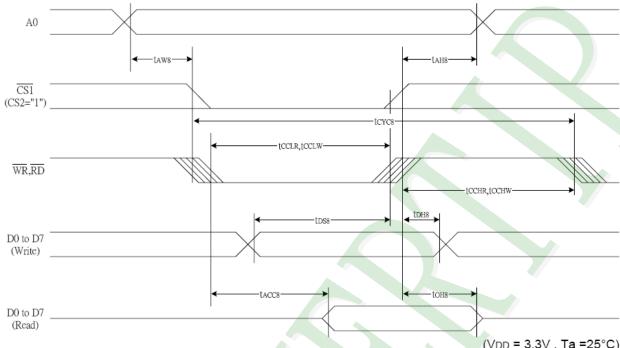

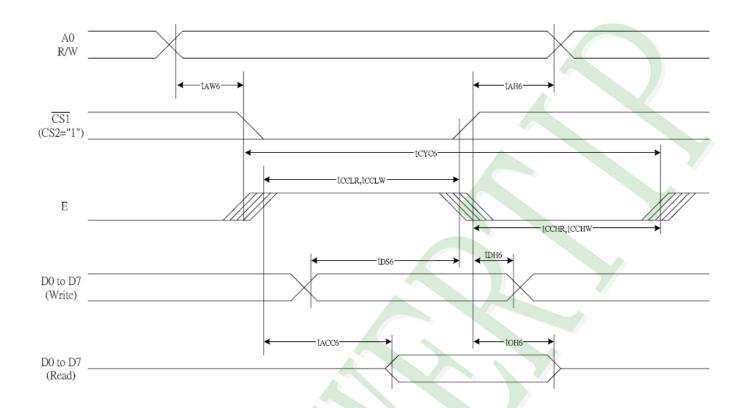

#### System Bus Read/Write Characteristics 1 (For the 8080 Series MPU)

|                              |          |                  |             | _      | 3∨ , Ia =25 | , ()  |

|------------------------------|----------|------------------|-------------|--------|-------------|-------|

| Item                         | Signal   | Symbol Condition |             | Rating |             | Units |

| item                         | Olgilai  | Symbol           | Condition   | Min.   | Max.        | Units |

| Address hold time            |          | t <sub>АН8</sub> |             | 0      | _           |       |

| Address setup time           | A0       | t <sub>AW8</sub> |             | 0      | _           |       |

| System cycle time            |          | tcyc8            |             | 240    | _           |       |

| Enable L pulse width (WRITE) | WR       | tcclw            |             | 80     | _           |       |

| Enable H pulse width (WRITE) | VVIX     | <b>t</b> cchw    |             | 80     | _           |       |

| Enable L pulse width (READ)  | RD       | tcclr            |             | 140    | _           | Ns    |

| Enable H pulse width (READ)  | , KD     | tcchr            |             | 80     |             |       |

| WRITE Data setup time        |          | t <sub>DS8</sub> |             | 40     | _           |       |

| WRITE Address hold time      | D0 to D7 | t <sub>DH8</sub> |             | 10     | _           | ]     |

| READ access time             | DU 10 D7 | tACC8            | CL = 100 pF | _      | 70          | ]     |

| READ Output disable time     |          | tонв             | CL = 100 pF | 5      | 50          |       |

<sup>\*1</sup> The input signal rise time and fall time (tr, tr) is specified at 15 ns or less. When the system cycle time is extremely fast,  $(t_r + t_f) \le (t_{CYC8} - t_{CCLW} - t_{CCHW})$  for  $(t_r + t_f) \le (t_{CYC8} - t_{CCLR})$  are specified.

<sup>\*2</sup> All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3</sup> toolw and tools are specified as the overlap between /CS1 being "L" (CS2 = "H") and /WR and /RD being at the "L" level.

#### System Bus Read/Write Characteristics 2 (For the 6800 Series MPU)

(VDD = 3.3 V , Ta = 25°C

|                              |          |                  |             | . \    | V , Ta = 25 | )     |

|------------------------------|----------|------------------|-------------|--------|-------------|-------|

| Item                         | Signal   | Symbol Condition |             | Rating |             | Units |

| Item                         | Olgital  | Symbol           | Condition   | Min.   | Max.        | Units |

| Address hold time            |          | <b>t</b> AH6     |             | 0      | _           |       |

| Address setup time           | A0       | taw6             |             | 0      | _           |       |

| System cycle time            |          | tcyc6            |             | 240    | _           |       |

| Enable L pulse width (WRITE) | WR       | tewLW            |             | 80     | _           |       |

| Enable H pulse width (WRITE) | VVK      | tewnw            |             | 80     | _           | ]     |

| Enable L pulse width (READ)  | RD       | tewlr            |             | 80     | _           | ns    |

| Enable H pulse width (READ)  | , KD     | tewhr            |             | 140    |             | ]     |

| WRITE Data setup time        |          | tos6             |             | 40     | _           | ]     |

| WRITE Address hold time      | D0 to D7 | t <sub>DH6</sub> |             | 10     | _           |       |

| READ access time             | ט נט טי  | tacc6            | CL = 100 pF | _      | 70          | ]     |

| READ Output disable time     |          | <b>t</b> он6     | CL = 100 pF | 5      | 50          |       |

<sup>\*1</sup> The input signal rise time and fall time  $(t_r, t_f)$  is specified at 15 ns or less. When the system cycle time is extremely fast,  $(t_r + t_f) \le (t_{CYC6} - t_{EWLW} - t_{EWHW})$  for  $(t_r + t_f) \le (t_{CYC6} - t_{EWLR} - t_{EWHR})$  are specified.

<sup>\*2</sup> All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3</sup> tewlw and tewlr are specified as the overlap between CS1 being "L" (CS2 = "H") and E.

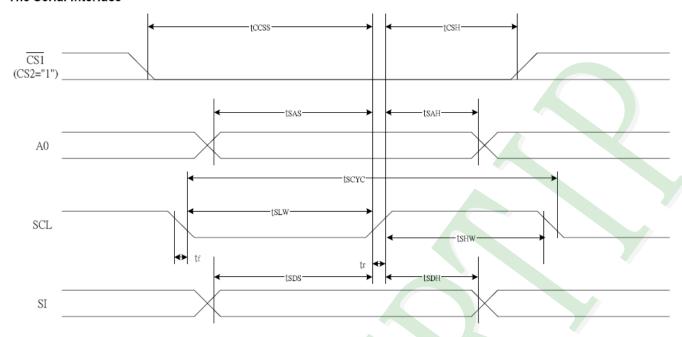

#### The Serial Interface

(VDD = 3.3V, Ta =25°C)

| Item                | Signal Symbol Condition |        | Condition | Rating |      | Units |

|---------------------|-------------------------|--------|-----------|--------|------|-------|

| Item                | Signal                  | Symbol | Condition | Min.   | Max. | Units |

| Serial Clock Period |                         | Tscyc  |           | 50     | _    |       |

| SCL "H" pulse width | SCL                     | Tshw   |           | 25     | _    |       |

| SCL "L" pulse width |                         | Tslw   |           | 25     | _    |       |

| Address setup time  | A0                      | Tsas   |           | 20     | _    |       |

| Address hold time   | AU                      | Tsah   |           | 10     | _    | ns    |

| Data setup time     | 2                       | Tsds   |           | 20     | _    |       |

| Data hold time      | SI                      | Tsph   |           | 10     | _    |       |

| CS-SCL time         | cs                      | Tcss   |           | 20     | _    |       |

| CS-SCL time         | 05                      | Tcsh   |           | 40     | _    |       |

- \*1 The input signal rise and fall time (tr, tf) are specified at 15 ns or less.

- $^{\ast}2$  All timing is specified using 20% and 80% of VDD as the standard.

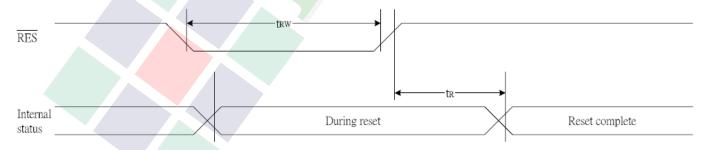

#### **Reset Timing**

$(V_{DD} = 3.3V, Ta = -40 \text{ to } 85^{\circ}C)$

| Item                  | Signal | Symbol     | Condition | ·    | Rating |      | Unito |

|-----------------------|--------|------------|-----------|------|--------|------|-------|

| item                  | Signal | Syllibol   | Condition | Min. | Тур.   | Max. | Units |

| Reset time            |        | <b>t</b> R |           | _    | -      | 0.5  | us    |

| Reset "L" pulse width | /RES   | trw        |           | 0.5  | _      | -    | us    |

## 2.4Power supply for LCD module

## 3. QUALITY ASSURANCE SYSTEM

## 3.1 Quality Assurance Flow Chart

# 3.2 Inspection Specification

- ◆Scope: The document shall be applied to LCD Module for Monotype and Color STN(Ver. B01).

- ◆Inspection Standard : MIL-STD-105E Table Normal Inspection Single Sampling Level Ⅱ.

- ◆Equipment : Gauge · MIL-STD · Powertip Tester · Sample

- ◆Defect Level: Major Defect AQL: 0.4; Minor Defect: AQL: 1.5.

- **♦**OUT Going Defect Level : Sampling .

- ◆Manner of appearance test :

- (1). The test be under 20W×2 fluorescent light 'and distance of view must be at 30 cm.

- (2). Standard of inspection: (Unit: mm)

- (3). The test direction is base on about around 45° of vertical line. (Fig. 1)

- (4). Definition of area . (Fig. 2)

Fig.1

Fig. 2 A area: viewing area

### ◆ Specification:

| NO | Item               | Criterion                                                               | Level |

|----|--------------------|-------------------------------------------------------------------------|-------|

|    |                    | 1. 1 The part number is inconsistent with work order of Production.     | Major |

| 01 | Product condition  | 1. 2 Mixed production types.                                            | Major |

|    |                    | 1. 3 Assembled in inverse direction.                                    | Major |

| 02 | Quantity           | 2. 1 The quantity is inconsistent with work order of production.        | Major |

| 03 | Outline dimension  | 3. 1 Product dimension and structure must conform to Structure diagram. | Major |

|    |                    | 4. 1 Missing line character and icon.                                   | Major |

|    |                    | 4. 2 No function or no display.                                         | Major |

| 04 | Electrical Testing | 4, 3 Output data is error.                                              | Major |

|    |                    | 4. 4 LCD viewing angle defect.                                          | Major |

|    |                    | 4. 5 Current consumption exceeds product specifications.                | Major |

| NO  | Item                                                                                                                                                               | C                                                                                                                                                                             | Criterion |                      |       | Level    |       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|-------|----------|-------|

|     | Black or white dot \ scratch \ contamination                                                                                                                       | <ul> <li>5. 1 Round type:</li> <li>5. 1. 1 display only:</li> <li>• White and black spots on</li> <li>4 white or black spots pr</li> <li>• Densely spaced: NO more</li> </ul> | esent.    |                      |       |          | ,     |

|     | Round type                                                                                                                                                         | 5. 1. 2 Non-display :  Dimension (diameter : Φ)                                                                                                                               |           | Acceptance<br>A area | (Q't  |          | 2//   |

|     |                                                                                                                                                                    | $\Phi \leq 0.10$                                                                                                                                                              |           | ept no dense         | В     | area     |       |

| 0.5 | $\begin{array}{c c} X & \\\hline Y & \\\hline \end{array}$                                                                                                         | $0.10 < \Phi \leq 0.20$                                                                                                                                                       |           | 3                    |       |          | 3.5.  |

| 05  | <b>→</b>                                                                                                                                                           | $0.20 < \Phi \leq 0.30$                                                                                                                                                       |           | 2                    | J     | Ignore   | Minor |

|     | $\Phi = (x+y)/2$                                                                                                                                                   | Total quantity                                                                                                                                                                |           | 4                    |       |          |       |

|     |                                                                                                                                                                    | 5. 1. 3 Line type:  Dimension                                                                                                                                                 | Y         | Accep                | otano | e (Q'ty) |       |

|     | Line type                                                                                                                                                          | Length (L) Width (W)                                                                                                                                                          |           | A area               |       | B area   |       |

|     | $\begin{array}{c c} & & \downarrow & W \\ \hline & \downarrow & W \\ \hline & \downarrow & \downarrow & \\ \hline & & \downarrow & \\ \hline & & & \\ \end{array}$ | L $\leq$ 3. 0 0. 03 < W $\leq$ 0 L $\leq$ 2. 5 0. 05 < W $\leq$ 0                                                                                                             | 0. 05     | Accept no de         | nse   | Ignore   |       |

|     |                                                                                                                                                                    | W >0                                                                                                                                                                          | . 075     | As                   | roun  | d type   |       |

|     |                                                                                                                                                                    | Dimension                                                                                                                                                                     |           | Acceptan             | ce (Q |          |       |

|     |                                                                                                                                                                    | (diameter : Φ)                                                                                                                                                                |           | A area               |       | B area   |       |

|     | Polarizer                                                                                                                                                          | $\Phi \le 0.20$ $0.20 < \Phi \le 0.50$                                                                                                                                        | Ac        | ccept no dense       |       |          |       |

| 06  | Bubble                                                                                                                                                             | $0.50 < \Phi \le 1.00$                                                                                                                                                        |           | 2                    |       | Ignore   | Minor |

|     |                                                                                                                                                                    | Φ > 1.00                                                                                                                                                                      |           | 0                    |       |          |       |

|     |                                                                                                                                                                    | Total quantity                                                                                                                                                                |           | 4                    |       |          |       |

|     |                                                                                                                                                                    |                                                                                                                                                                               | I .       |                      |       |          |       |

| NO | Item                  | Criterion                                                                                                                                         | Level |

|----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    |                       | Symbols:  X: The length of crack Z: The thickness of crack t: The thickness of glass  X: The width of crack W: terminal length a: LCD side length |       |

|    |                       | 7.1 General glass chip: 7.1.1 Chip on panel surface and crack between panels:                                                                     |       |

| 07 | The crack of<br>glass | SP SP [NG]                                                                                                                                        | Minor |

|    |                       | X Y Z                                                                                                                                             |       |

|    |                       | ≤ a Crack can't enter viewing area ≤1/2 t                                                                                                         |       |

|    |                       | ≤ a Crack can't exceed the half of SP width. 1/2 t < Z ≤2 t                                                                                       |       |

|    |                       |                                                                                                                                                   |       |

| NO | Item         | Criterion                                                                                                   | Level |

|----|--------------|-------------------------------------------------------------------------------------------------------------|-------|

|    |              | Symbols:  X: The length of crack Z: The thickness of crack t: The thickness of glass  7. 1. 2 Corner crack: |       |

|    |              | X Y Z                                                                                                       |       |

|    |              | ≤1/5 a Crack can't enter viewing area Z ≤ 1/2 t                                                             |       |

| 07 | The crack of |                                                                                                             | 3.5   |

| 01 | glass        | 7.2 Protrusion over terminal:                                                                               | Minor |

|    |              | 7. 2. 1 Chip on electrode pad:                                                                              |       |

|    |              | X Y Z X Y Z                                                                                                 |       |

|    |              | X                                                                                                           |       |

|    | X            | X Y Z                                                                                                       |       |

|    |              | Front $\leq$ a $\leq$ 1/2 W $\leq$ t                                                                        |       |

|    |              | Back Neglect                                                                                                |       |

|    |              |                                                                                                             |       |

| NO | Item                  | Criterion                                                                                                                                         | Level |

|----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    |                       | Symbols:  X: The length of crack Z: The thickness of crack t: The thickness of glass  X: The width of crack W: terminal length a: LCD side length |       |

|    |                       | 7.2.2 Non-conductive portion:                                                                                                                     |       |

| 07 | The crack of<br>glass | X Y Z  ≤1/3 a ≤W ≤t  O If the chipped area touches the ITO terminal, over 2/3 of the ITO must remain and be inspected according to electrode      | Minor |

|    |                       | terminal specifications.  7. 2. 3 Glass remain: $X$ $Y$                                                       |       |

| NO | Item                  | Criterion                                                                           | Level |

|----|-----------------------|-------------------------------------------------------------------------------------|-------|

| 08 |                       | 8. 1 Backlight can't work normally.                                                 | Major |

|    | Backlight<br>elements | 8. 2 Backlight doesn't light or color is wrong.                                     | Major |

|    |                       | 8. 3 Illumination source flickers when lit.                                         | Major |

|    | General               | 9. 1 Pin type must match type in specification sheet.                               | Major |

|    |                       | 9. 2 No short circuits in components on PCB or FPC.                                 | Major |

| 09 |                       | 9. 3 Product packaging must the same as specified on packaging specification sheet. | Minor |

|    |                       | 9. 4 The folding and peeled off in polarizer are not acceptable.                    | Minor |

|    |                       | 9. 5 The PCB or FPC between B/L assembled distance (PCB or FPC) is ≤1.5 mm.         | Minor |

# 4. RELIABILITY TEST

# 4.1 Reliability Test Condition

| NO. | TEST ITEM                                           | TEST CONDITION                                                                                                                                                                                                                                                                                                                                                                                  |                                |  |  |

|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| 1   | High Temperature<br>Storage Test                    | Keep in 80 ±2℃ 96 hrs Surrounding temperature, then storage at normal condition 4hrs.                                                                                                                                                                                                                                                                                                           |                                |  |  |

| 2   | Low Temperature<br>Storage Test                     | Keep in -30 ±2°C 96 hrs<br>Surrounding temperature, ther<br>4hrs.                                                                                                                                                                                                                                                                                                                               | storage at normal condition    |  |  |

| 3   | High Temperature /<br>High Humidity<br>Storage Test | 4hrs.<br>(Excluding the polarizer)                                                                                                                                                                                                                                                                                                                                                              | en storage at normal condition |  |  |

| 4   | Temperature Cycling<br>Storage Test                 | -30°C→ +25°C → 80°C → +25°C  (30mins) (5mins) (30mins) (5mins)  10 Cycle  Surrounding temperature, then storage at normal condition 4hrs.                                                                                                                                                                                                                                                       |                                |  |  |

| 5   | ESD Test                                            | Air Discharge: Apply 2 KV with 5 times Discharge for each polarity +/-  1. Temperature ambiance : 15°C ~35°C 2. Humidity relative : 30%~60% 3. Energy Storage Capacitance(Cs+Cd) : 150pF±10% 4. Discharge Resistance(Rd) : 330 Ω±10% 5. Discharge, mode of operation : Single Discharge (time between successive discharges at least 1 sec)  (Tolerance if the output voltage indication : ±5%) |                                |  |  |

| 6   | Vibration Test<br>(Packaged)                        | <ol> <li>Sine wave 10~55 Hz frequency (1 min/sweep)</li> <li>The amplitude of vibration :1.5 mm</li> <li>Each direction (X ⋅ Y ⋅ Z) duration for 2 Hrs</li> </ol>                                                                                                                                                                                                                               |                                |  |  |

| 7   | Drop Test<br>(Packaged)                             | Packing Weight (Kg 0 ~ 45.4 45.4 ~ 90.8 90.8 ~ 454 Over 454  Drop Direction : %1 corner / 3 e                                                                                                                                                                                                                                                                                                   | 122<br>76<br>61<br>46          |  |  |

### 5. PRECAUTION RELATING PRODUCT HANDLING

### **5.1 SAFETY**

- 5.1.1 If the LCD panel breaks, be careful not to get the liquid crystal to touch your skin.

- 5.1.2 If the liquid crystal touches your skin or clothes, please wash it off immediately by using soap and water.

#### 5.2 HANDLING

- 5.2.1 Avoid any strong mechanical shock which can break the glass.

- 5.2.2 Avoid static electricity which can damage the CMOS LSI—When working with the module, be sure to ground your body and any electrical equipment you may be using.

- 5.2.3 Do not remove the panel or frame from the module.

- 5.2.4 The polarizing plate of the display is very fragile. So , please handle it very carefully ,do not touch , push or rub the exposed polarizing with anything harder than an HB pencil lead (glass , tweezers , etc.)

- 5.2.5 Do not wipe the polarizing plate with a dry cloth, as it may easily scratch the surface of plate.

- 5.2.6 Do not touch the display area with bare hands, this will stain the display area.

- 5.2.7 Do not use ketonics solvent & aromatic solvent. Use with a soft cloth soaked with a cleaning naphtha solvent.

- 5.2.8 To control temperature and time of soldering is 320±10°C and 3-5 sec.

- 5.2.9 To avoid liquid (include organic solvent) stained on LCM.

### **5.3 STORAGE**

- 5.3.1 Store the panel or module in a dark place where the temperature is 25°C ±5°C and the humidity is below 65% RH.

- 5.3.2 Do not place the module near organics solvents or corrosive gases.

- 5.3.3 Do not crush, shake, or jolt the module.

### **5.4 TERMS OF WARRANTY**

5.4.1 Applicable warrant period

The period is within thirteen months since the date of shipping out under normal using and storage conditions.

#### 5.4.2 Unaccepted responsibility

This product has been manufactured to your company's specification as a part for use in your company's general electronic products. It is guaranteed to perform according to delivery specifications. For any other use apart from general electronic equipment, we cannot take responsibility if the product is used in nuclear power control equipment, aerospace equipment, fire and security systems or any other applications in which there is a direct risk to human life and where extremely high levels of reliability are required.

Check Approve Contact LCM包裝規格書 Ver.001 LCM Packaging Specifications Documents NO. JPKG-PE12864WRF-004HC1Q Ryan Terry Sally (For Tray) 1.包裝材料規格表 (Packaging Material): (per carton) No. Item Model Dimensions (mm) 1Pcs Weight Quantity Total Weight PE12864WRF-004HC1Q 1 成品 (LCM) 80.0 X 54.0 144 0.025 3.6 2 多層薄膜(1)POF 19"X350X0.015 6 OTFILM0BA03ABA 3 295 X 245 X 18.8 32 TRAY 盤 (2)Tray TY12806404TZBA 0.08 2.56 4 內盒(3)Product Box BX31025580AABA 310 X255 X 86 8 1.6 0.2 5 海綿墊(4)Foam Rubber Cushion OTFOAM00006ABA 290 X 240 X 10 0.02 16 0.32 6 外紙箱(5)Carton 527 X 325 X 360 BX52732536CCBA 0.83 0.83 7 8 9 Kg±10% 2. 一整箱總重量 (Total LCD Weight in carton ): 3. 單箱數量規格表 (Packaging Specifications and Quantity): (1)LCM quantity per box : no per tray x no of tray 6 18 (2)Total LCM quantity in carton: quantity per box x no of boxes 18 144 Use empty tray 空盤 (4)海綿墊 Foam Rubber Cushion (1)多層薄膜 POF Put products into the tray (2)TRAY 盤 Tray (4)海綿墊 Foam Rubber Cushion (5)外紙箱 Carton Tray stacking (3)內盒 Product Box 特 記 事 項 (REMARK) 1. Label Specifications: 斜角 Detail B 參照"成品包裝點檢作業標準書"內容 圓角 Tray 1 2.TRAY盤相疊時,需旋轉180度,請詳見B視圖 Rotate tray 180 degrees and place on top of stack. Check the tray stack using Fig. B.