**PROPRIETARY NOTE :** THIS SPECIFICATION IS THE PROPERTY OF BOE AND SHALL NOT BE REPRODUCED OR COPIED WITHOUT THE WRITTEN PERMISSION OF BOE AND MUST BE RETURNED TO BOE UPON ITS REQUEST

# **Approval Sheet**

Preliminary specification

### □ Final specification

| Customer Name                                           | * * * * *         |

|---------------------------------------------------------|-------------------|

| Product Description 3.5inch 1440RGB*1600 TFT-LCD Module |                   |

| Version                                                 | Pre.0             |

| Supplier                                                | BOE               |

| Module Code                                             | VS035ZSM-NW0-69P0 |

ORDOS YUANSHENG OPTOELECTRONICS TECHNOLOGY CO.,LTD.

B2006-5006-O (3/3)

P0

# **Product Specification**

Product Name : 3.5" TFT-LCD Module

Model Name : VS035ZSM-NW0-69P0

Description : 3.5" 1440RGB×1600 16.7M Color

| PREPARED BY | CHECKED BY | APPROVALED BY |

|-------------|------------|---------------|

|             |            |               |

|             |            |               |

# ORDOS YUANSHENG OPTOELECTRONICS TECHNOLOGY CO.,LTD.

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 2 OF 34 |

B2006-5006-O (3/3)

| BOE |

|-----|

|-----|

2017.03.20

# **Revision History**

| REV. | ECN NO. | DESCRIPTION OF CHANGES | DATE       | PREPARED |

|------|---------|------------------------|------------|----------|

| P0   | -       | Initial Release        | 2017.03.20 | GONG LEI |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         | 70                     |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

SPEC. NUMBER<br/>SXXX-XXXXSPEC TITLEPAGESXXX-XXXXVS035ZSM-NW0-69P0 Product Specification3 OF 34

B2006-5006-O (3/3)

ISSUE DATE

2017.03.20

# Contents

| NO.   |                | ITEMS                                 | PAGE   |

|-------|----------------|---------------------------------------|--------|

| 1.0   | General Des    | cription                              | 6      |

| 1.1   | Introduction   |                                       | 6      |

| 1.2   | Feature        |                                       | 7      |

| 1.3   | Application    |                                       | 7      |

| 1.4   | General spec   | ification                             | 8      |

| 2.0   | Absolute Ma    | ximum Ratings                         | 9      |

| 3.0   | Electrical Sp  | ecifications                          | 10     |

| 3.1   | TFT-LCD Par    | iel                                   | 10     |

| 3.2   | Back-light Un  | it                                    | 11     |

| 4.0   | Optical Spec   | ifications                            | 12     |

| 4.1   | Overview       |                                       | 12     |

| 4.2   | Optical specif | ications                              | 12     |

| 5.0   | Interface Cor  | nnection                              | 16     |

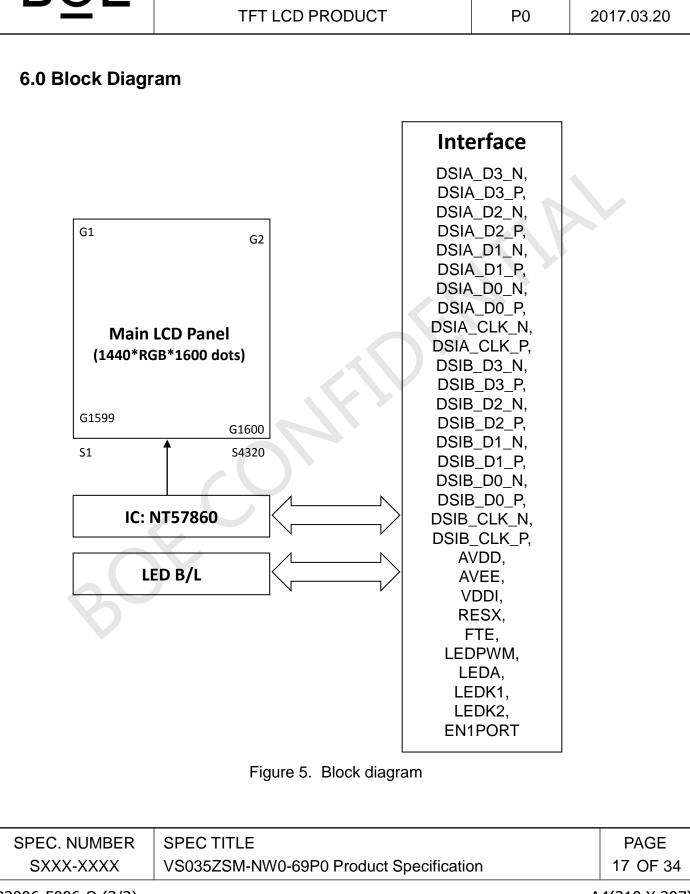

| 6.0   | Block Diagra   | m                                     | 17     |

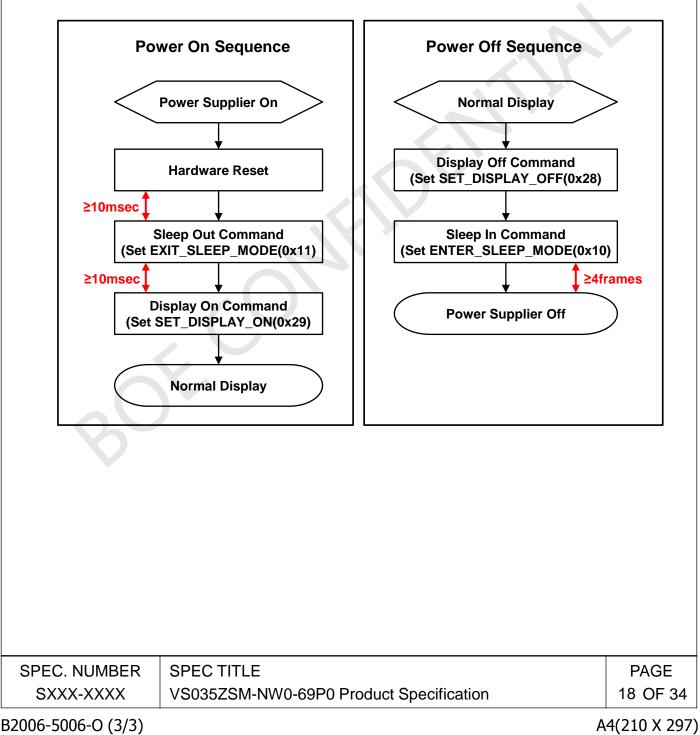

| 7.0   | Timing Chara   | acteristics                           | 18     |

| 7.1   | Power on/off   | sequence                              | 18     |

| 7.2   | Reset Timing   | Sequence                              | 21     |

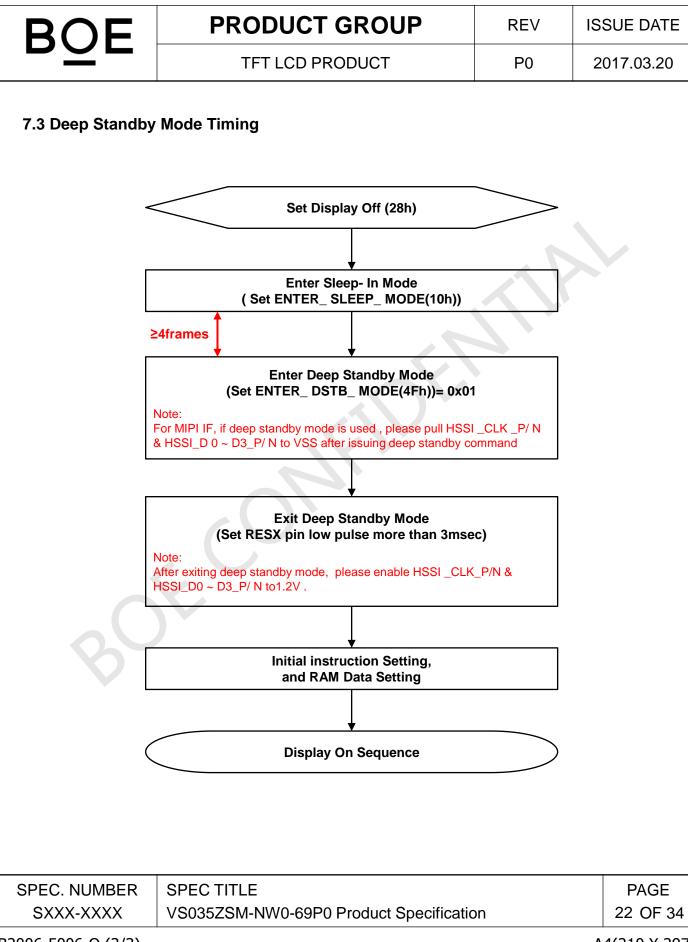

| 7.3   | Deep Standby   | / Mode Timing                         | 22     |

| 7.4   | MIPI Interface | e Characteristics                     | 23     |

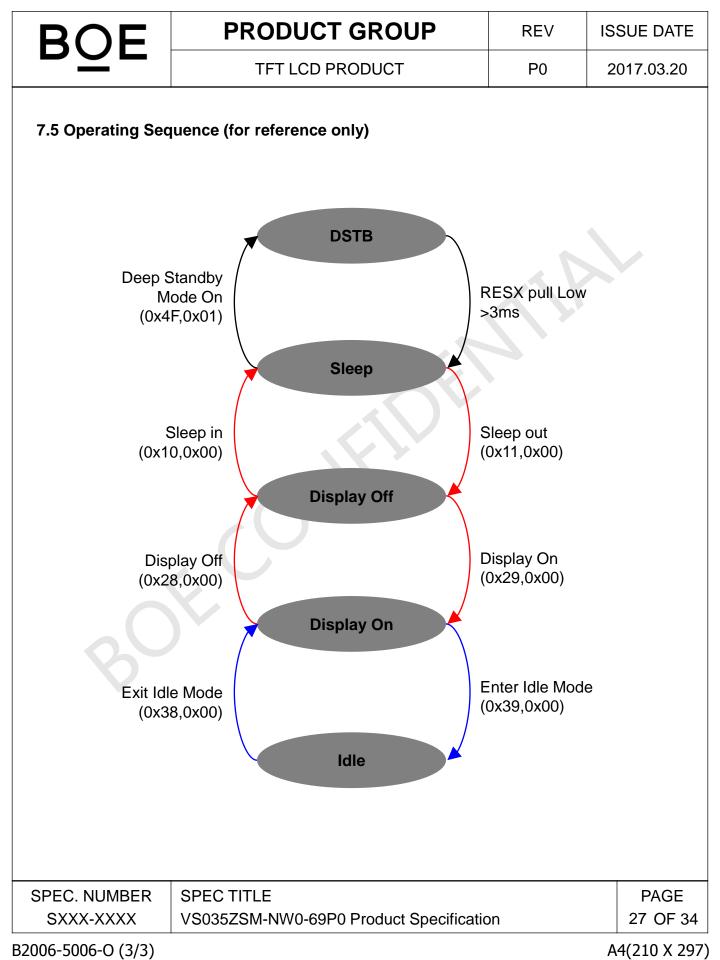

| 7.5   | Operating Sec  | quence                                | 27     |

| 7.6   | Initial Code S | etting                                | 28     |

| SPEC. | NUMBER SF      | PECTITLE                              | PAGE   |

| SXXX  | K-XXXX VS      | 035ZSM-NW0-69P0 Product Specification | 4 OF 3 |

| B | <u>C</u> | Ε |

|---|----------|---|

|   |          |   |

EV ISSUE DATE

2017.03.20

| NO.  | ITEMS                      | PAGE |

|------|----------------------------|------|

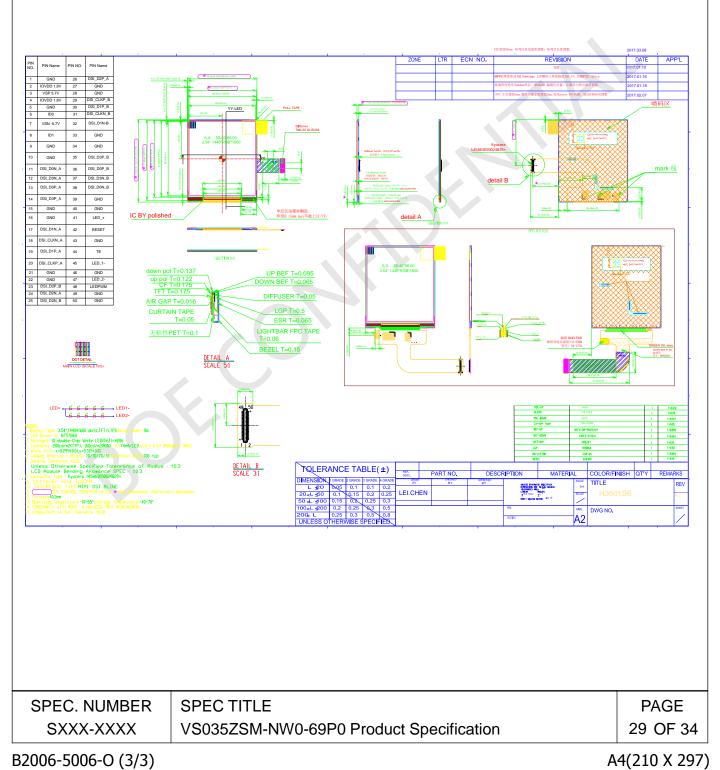

| 8.0  | Mechanical Characteristics | 29   |

| 9.0  | Reliability Test           | 30   |

| 10.0 | Packing Information        | 31   |

| 10.1 | Packing Description        | 31   |

| 10.2 | Packing Procedure          | 32   |

| 10.3 | Box Label                  | 33   |

| 11.0 | Handing & Cautions         | 34   |

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 5 OF 34 |

# **1.0 GENERAL DESCRIPTION**

## **1.1 Introduction**

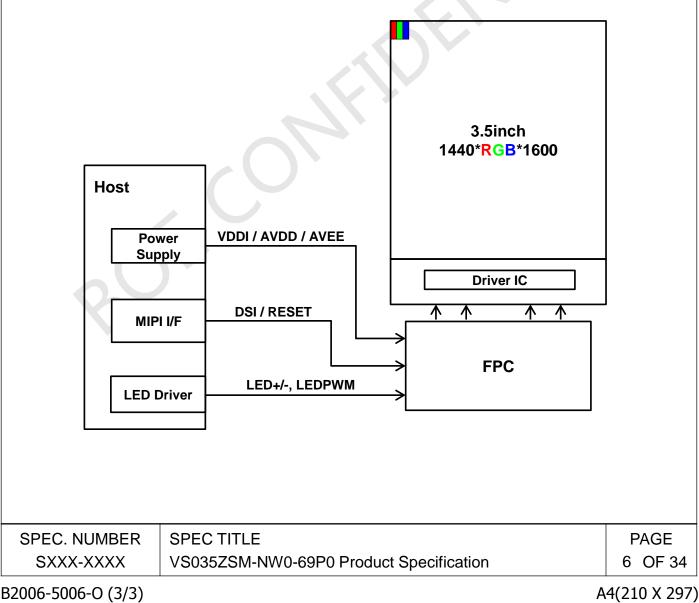

The 3.5inch TFT-LCD Module is a Color Active Matrix TFT LCD panel using LTPS (Low Temperature Poly-silicon) TFT's (Thin Film Transistors) as an active switching devices. This module has a 3.5 inch diagonally measured active area with 1440\*1600 resolutions (1440 horizontal by 1600 vertical pixel array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16.7M colors. The TFT-LCD panel used for this module is adapted for a low reflection and higher color type.

| BOE | PRODUCT GROUP   | REV | ISSUE DATE |

|-----|-----------------|-----|------------|

|     | TFT LCD PRODUCT | P0  | 2017.03.20 |

## 1.2 Features

- High PPI

- Fast response time

- High frame ratio

- High luminance, low reflection and wide viewing angle

- RoHS、Halogen Free Compliant

## **1.3 Application**

- Virtual Reality Device

- Augmented Reality Device

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 7 OF 34 |

B2006-5006-O (3/3)

2017.03.20

## **1.4 General Specification**

< Table 1. General Specifications >

| Parameter             | Specification                           | Unit   | Remark     |

|-----------------------|-----------------------------------------|--------|------------|

| Display method        | Active matrix TFT                       |        |            |

| Display mode          | Transmission mode, Normally black       |        |            |

| Screen size           | 3.5 (88.79mm)                           | inch   | diagonally |

| Number of pixels      | 1440(H) × 1600(V)                       | pixels | 615 ppi    |

| Active area           | 59.4(H) × 66.0(V)                       | mm     |            |

| Pixel pitch           | 13.75(H) × 41.25(V)                     | um     |            |

| Pixel arrangement     | RGB stripe                              |        |            |

| Display colors        | 16.7M                                   | colors | 8bit       |

| NTSC Ratio            | 85%                                     |        |            |

| LCM Outline Dimension | 62.2(H) $	imes$ 73.6(V) $	imes$ 1.7 (T) | mm     | Note 1)    |

| LCM Weight            | 17.0 ±2.0                               | gram   | Note 1)    |

| Driver IC             | NT57860                                 |        |            |

| Interface             | MIPI DSI (Video Mode)                   |        |            |

| Surface Treatment     | HC, ≥3H                                 |        |            |

## Note:

1) Protection film is not included.

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 8 OF 34 |

P0

# 2.0 ABSOLUTE MAXIMUM RATINGS

| < Table 2. Absolute Maximum Ratings> | [Ta =25±2 ℃] |

|--------------------------------------|--------------|

|--------------------------------------|--------------|

| Items                                   | Symbol           | Rating            | Unit | Remark                  |

|-----------------------------------------|------------------|-------------------|------|-------------------------|

| Logic voltage                           | VDDI             | -0.3 to +1.8      | V    |                         |

| Positive Analog<br>Power Supply Voltage | AVDD             | -0.3 to +5.7      | V    |                         |

| Negative Analog<br>Power Supply Voltage | AVEE             | -5.7 to +0.3      | V    |                         |

| LED forward current                     | I <sub>LED</sub> | 50                | mA   | each LED<br>10% on duty |

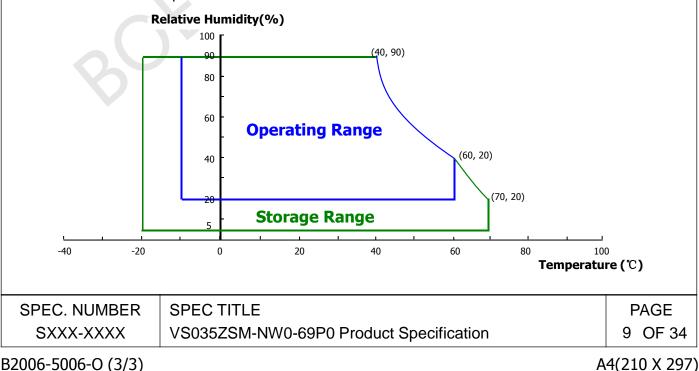

| Storage temperature                     | T <sub>STG</sub> | -40 to +70        | °C   |                         |

| Operation temperature                   | T <sub>OPR</sub> | -10 to +55        | °C   |                         |

| Humidity<br>(ambient temeprature=Ta)    |                  | Ta≤55℃, 90% RH Ma | ax.  |                         |

Note 1: If the module exceeds the absolute maximum ratings, it may be damaged permanently. Also, if the module operated with the absolute maximum ratings for a long time, its reliability may drop. It is not allowed for any of these ratings to be exceeded. Make sure all the design characte ristics are adequate before the panel is initialed.

Note 2: Temperature and relative humidity range are shown in the figure below. Wet bulb temperature should be 55  $^\circ\!C$  max. and no condensation of water.

< Table 3, I CD Panel Electrical Specifications >

P0

[Ta =25 + 2 °C]

# 3.0 ELECTRICAL SPECIFICATIONS

## 3.1 TFT LCD Panel

|                           | < Table 3. LCD Panel Electrical Specifications > $[Ta = 25 \pm 2 \ C]$ |                   |          |      |          |      |        |  |

|---------------------------|------------------------------------------------------------------------|-------------------|----------|------|----------|------|--------|--|

| Items                     |                                                                        | Symbol            | Min.     | Тур. | Max.     | Unit | Remark |  |

| Logic vo                  | ltage                                                                  | VDDI              | 1.7      | 1.8  | 1.9      | V    |        |  |

| Positive A<br>Power Suppl |                                                                        | AVDD              | 5.4      | 5.7  | 6.0      | V    | Note 1 |  |

| Negative A<br>Power Suppl | •                                                                      | AVEE              | -6.0     | -5.7 | -5.4     | V    |        |  |

| Frame F                   | Ratio                                                                  | FPS               | -        | 90   |          | Hz   |        |  |

| Input signal              | High level                                                             | V <sub>IH</sub>   | 0.7×VDDI |      | VDDI     | V    |        |  |

| voltage                   | Low level                                                              | V <sub>IL</sub>   | VSSI     |      | 0.3×VDDI | V    |        |  |

| Output signal             | High level                                                             | V <sub>OH</sub>   | 0.8×VDDI | -    | VDDI     |      |        |  |

| voltage                   | Low level                                                              | Vol               | VSSI     | -    | 0.2×VDDI |      |        |  |

|                           |                                                                        | I <sub>VDDI</sub> |          | 70   | -        | mA   |        |  |

| Current con:              | Current consumption                                                    |                   | -        | 10.5 | -        | mA   | Note 2 |  |

| (                         |                                                                        | I <sub>AVEE</sub> | -        | -9.5 | -        | mA   |        |  |

| Driver IC ESD             |                                                                        | НВМ               | - 2      | -    | +2       | kV   |        |  |

| Diveric                   | , LOD                                                                  | MM                | -200     | -    | +200     | V    |        |  |

## Note 1:

The value can be adjusted by software to optimize display quality.

The operation is guaranteed under the recommended operating conditions only. The oper ation is not guaranteed if a quick voltage change occurs during operation. To prevent nois e, a bypass capacitor must be inserted into the line close to power pin. Please make sure all the design settings are used within this range before the panel is initialed.

Note 2:

Test pattern: All White Display

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 10 OF 34 |

2017.03.20

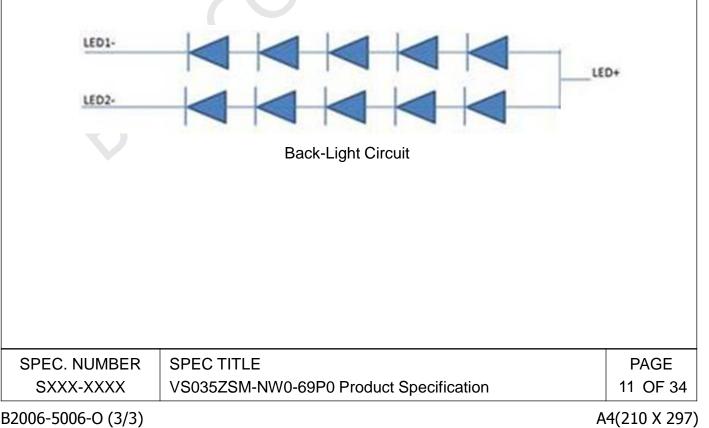

## 3.2 Back-light Unit

Ta=25+/-2°C

|                   |                 |      | 5 1  |      |      |        |

|-------------------|-----------------|------|------|------|------|--------|

| Items             | Symbol          | Min. | Тур. | Max. | Unit | Remark |

| Forward Current   | lf              | -    | 50   | -    | mA   | Note1  |

| Forward Voltage   | Vf              | -    | 6.5  | -    | V    | Note1  |

| Power Consumption | P <sub>BL</sub> | -    | 325  | -    | mW   | Note2  |

| LED Q'ty          |                 |      | 10   |      | Ea   |        |

- Note 1: The driving condition is defined for each LED chip.

- Note 2: The B/L power consumption is defined for the backlight module. the schematic drawing of the backlight unit is as the figure. The B/L power consumption is based on 10% on duty mode

- Ref. Total power consumption(max) depends on LED current/LED driver efficiency, etc.

# 4.0 OPTICAL SPECIFICATION

## 4.1 Overview

The optical characteristics should be measured in a dark room (ambient luminance≤ 1 lux and temperature =  $25\pm2^{\circ}$ C) with the equipment of Konica Minolta CA-310 and CS-2000 and test unit shall be located at an approximate distance 50cm from the LCD surface at a viewing angle of  $\theta$  and  $\Phi$  equal to  $0^{\circ}$ . The center of the measuring spot on the display su rface should stay fixed.

The operation should be under the recommended operating conditions.

## 4.2 Optical Specifications

| Item                                              |             | Symbol          | Condition            | Min. | Тур.  | Max. | Unit              | Remark |

|---------------------------------------------------|-------------|-----------------|----------------------|------|-------|------|-------------------|--------|

|                                                   | Horizontal  | θ3              |                      | -    | 70    | -    |                   |        |

|                                                   | HUHZUHIai   | θ <sub>9</sub>  | CR > 10              | -    | 70    | -    | 1                 | Note 4 |

| Viewing Angle                                     | Vertical    | θ <sub>12</sub> | CR > 10              | -    | 70    | -    | degree            | Note 1 |

|                                                   | Vertical    | θ <sub>6</sub>  |                      | -    | 70    | -    |                   |        |

| Color Ga                                          | amut (NTSC) |                 | $\theta = 0^{\circ}$ | -    | 85    | -    | %                 |        |

| Contrast Rat                                      | io          | CR              | $\theta = 0^{\circ}$ | -    | 600   | -    |                   | Note 2 |

| Luminance of White                                | Center      | Y <sub>w</sub>  | 0 00                 | 120  | 150   | -    | cd/m <sup>2</sup> | Note 3 |

| Luminance Uniformity                              | 5 Points    | ΔΥ5             | $\theta = 0^{\circ}$ | 80%  | 85%   | -    |                   | Note 4 |

|                                                   |             | Rx              |                      | -    | 0.66  | -    |                   |        |

|                                                   | Red         | Ry              |                      | -    | 0.372 | -    |                   | 1      |

|                                                   | 0           | Gx              |                      | -    | 0.275 | -    |                   |        |

| Chromaticity                                      | Green       | Gy              | 0 00                 | -    | 0.652 | -    |                   |        |

| (CIE 1931)                                        | Dive        | Bx              | $\theta = 0^{\circ}$ | -    | 0.15  | -    |                   | Note 5 |

|                                                   | Blue        | Ву              |                      | -    | 0.06  | -    |                   |        |

|                                                   | 14/1-14     | Wx              |                      | -    | 0.299 | -    |                   |        |

|                                                   | White       | Wy              |                      | -    | 0.315 | -    |                   |        |

| Response Tir<br>(G to G)                          | ne          | т               | $\theta = 0^{\circ}$ | -    | -     | 5    | ms                | Note 6 |

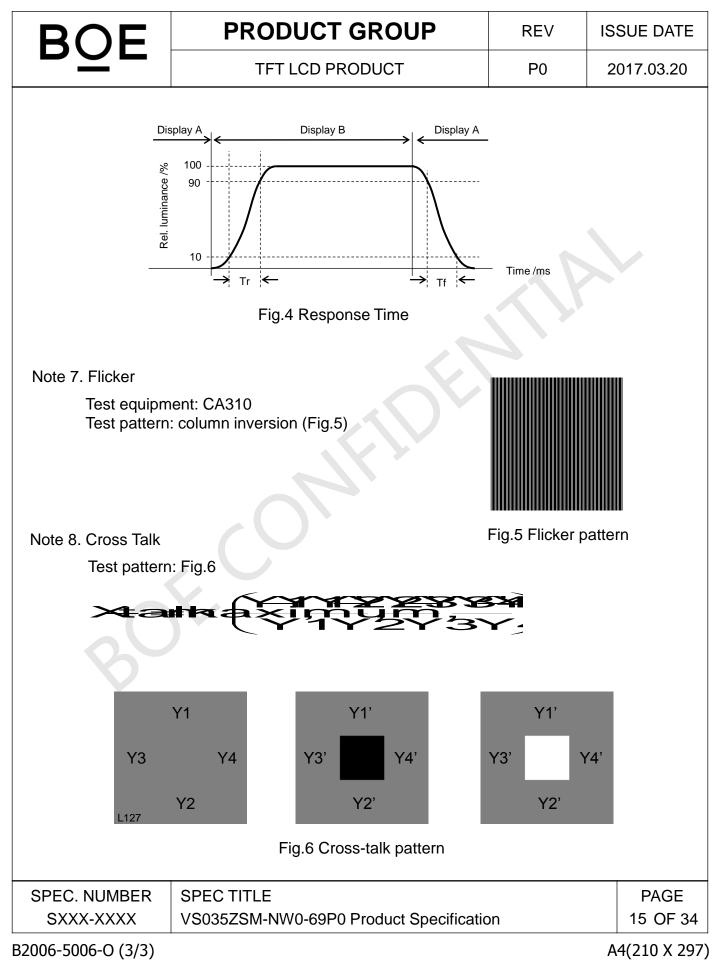

| Flicker                                           |             |                 | $\theta = 0^{\circ}$ | -    | -     | -30  | db                | Note 7 |

| Cross Talk                                        |             | СТ              | $\theta = 0^{\circ}$ | -    | -     | 2    | %                 | Note 8 |

|                                                   |             |                 |                      |      |       |      |                   |        |

| SPEC. NUMBER                                      | R SPE       | CTITLE          |                      |      |       |      |                   | PAGE   |

| SXXX-XXXX VS035ZSM-NW0-69P0 Product Specification |             |                 |                      |      | l     |      | 12 OF 3           |        |

<Table 5. Optical Specifications>

B2006-5006-O (3/3)

| Β | Ο | Ε |

|---|---|---|

|   |   |   |

P0

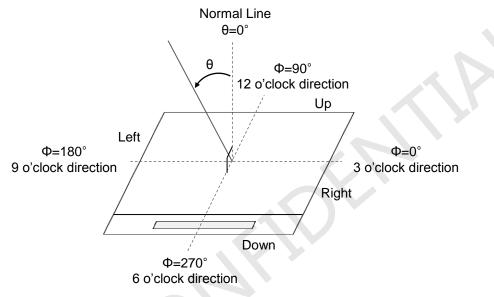

Note 1. Viewing angle is the angle at which the contrast ratio is greater than 10. The viewing angles are determined for the horizontal or 3, 9 o'clock direction and the vertical or 6, 12 o'clock direction with respect to the optical axis which is normal to the LCD surface (FIGURE 1).

Fig.1 Viewing angle measurement setup

Note 2. Contrast ratio measurements shall be made at viewing angle of  $\theta$ =0° and at the center of the LCD surface. Luminance shall be measured with all pixels in the view field set first to white, then to the dark (black) state (FIGURE 1). Contrast Ratio (CR) is defined mathematically.

Luminance when displaying a white raster

Luminance when displaying a black raster

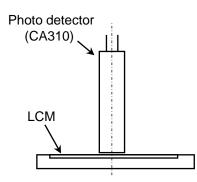

Note 3. Luminance of white is defined as luminance values of the center point across the LCD surface. Luminance shall be measured with all pixels in the view field set first to white. This measurement shall be taken at the locations shown in FIGURE 2 for a total of the measurements per display. The luminance is measured by CA310 when **the LED current is set at 50mA/ea and the backlight is under the 10% on duty mode.**

Note 4. The White luminance uniformity is then expressed as:

CR =

$\Delta Y$  = Minimum Luminance of 5 points / Maximum Luminance of 5 points (FIGURE 3).

|              |                                         | i        |

|--------------|-----------------------------------------|----------|

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 13 OF 34 |

B2006-5006-O (3/3)

Fig.2 Luminance, uniformity & chromaticity measurement setup

Fig.3 Luminance uniformity measurement setup

- Note 5. The color chromaticity is measured with all pixels first in red, green, blue and white. Measurements should be made at the center of the panel.

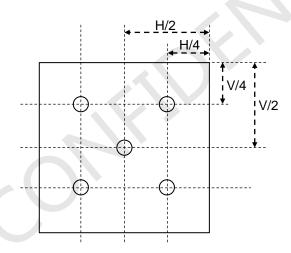

- Note 6. Definition of Response time.

The output signals of photo detector are measured when the input signals are switched between different display pattern (Gray-to-Gray). The response time is defined as the time interval **between the 10% and 90% of amplitudes** (Fig.4)

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 14 OF 34 |

B2006-5006-O (3/3)

## **5.0 INTERFACE CONNECTION**

The electronics interface connector is **Kyocera 145863050024829+** The connector interface pin assignments are listed in Table 6. <Table 6. Pin Assignments for the Interface Connector>

| NO. | Symbol         | Description              | NO. | Symbol     | Description                   |

|-----|----------------|--------------------------|-----|------------|-------------------------------|

| 1   | GND1           | Ground                   | 26  | DSI_D2P_A  | MIPI DSI port A data 2_P      |

| 2   | IOVDD          | 1.8V                     | 27  | GND        | Ground                        |

| 3   | VSP            | 5.7V                     | 28  | GND        | Ground                        |

| 4   | IOVDD          | 1.8V                     | 29  | DSI_CLKP_B | MIPI DSI port B clock_P       |

| 5   | GND            | Ground                   | 30  | DSI_D1P_B  | MIPI DSI port B data 1_P      |

| 6   | ID0            | GND                      | 31  | DSI_CLKN_B | MIPI DSI port B clock_N       |

| 7   | VSN            | -5.7V                    | 32  | DSI_D1N_B  | MIPI DSI port B data 1_N      |

| 8   | ID1            | IOVDD                    | 33  | GND        | Ground                        |

| 9   | GND            | Ground                   | 34  | GND        | Ground                        |

| 10  | GND            | Ground                   | 35  | DSI_D3P_B  | MIPI DSI port B data 3_P      |

| 11  | DSI_D0N_A      | MIPI DSI port A data 0_N | 36  | DSI_D0P_B  | MIPI DSI port B data 0_P      |

| 12  | DSI_D3N_A      | MIPI DSI port A data 3_N | 37  | DSI_D3N_B  | MIPI DSI port B data 3_N      |

| 13  | DSI_D0P_A      | MIPI DSI port A data 0_P | 38  | DSI_D0N_B  | MIPI DSI port B data 0_N      |

| 14  | DSI_D3P_A      | MIPI DSI port A data 3_P | 39  | GND        | Ground                        |

| 15  | GND            | Ground                   | 40  | GND        | Ground                        |

| 16  | GND            | Ground                   | 41  | LED +      | LED anode                     |

| 17  | DSI_D1N_A      | MIPI DSI port A data 1_N | 42  | RESET      | LCD reset signal (low active) |

| 18  | DSI_CLKN_<br>A | MIPI DSI port A clock_N  | 43  | GND        | Ground                        |

| 19  | DSI_D1P_A      | MIPI DSI port A data 1_P | 44  | TE         | Tearing effect output pin     |

| 20  | DSI_CLKP_<br>A | MIPI DSI port A clock_P  | 45  | LED 1-     | LED cathode 1                 |

| 21  | GND            | Ground                   | 46  | GND        | Ground                        |

| 22  | GND            | Ground                   | 47  | LED 2-     | LED cathode 2                 |

| 23  | DSI_D2P_B      | MIPI DSI port B data 2_P | 48  | LEDPWM     | LED PWM signal pin            |

| 24  | DSI_D2N_A      | MIPI DSI port A data 2_N | 49  | GND        | Ground                        |

| 25  | DSI_D2N_B      | MIPI DSI port B data 2_N | 50  | GND        | Ground                        |

#### Remark:

Port A&B are determined by the value of BA register : When BA Register is assigned to 07 ,only port A is valid When BA Register is assigned to 03, port A and B are valid.

VDDI is defined as "H" level and GND is defined as "L" level.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 16 OF 34 |

B2006-5006-O (3/3)

BOE

B2006-5006-O (3/3)

# 7.0 Timing Characteristics

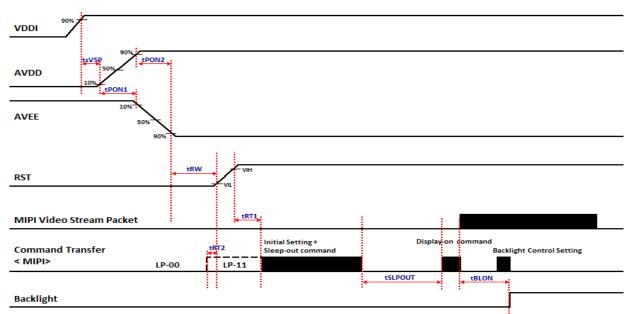

## 7.1 Power On/Off Sequence

The power supply ON/OFF setting for Display ON/OFF, Standby Set/Exit, and Sleep Set/Exit sequences is illustrated in figure below.

|     | PRODUCT GROUP   | REV | ISSUE DATE |

|-----|-----------------|-----|------------|

| DZL | TFT LCD PRODUCT | P0  | 2017.03.20 |

#### Power On Sequence

Note 1: After Sleep-Out Command, Driver IC will reload MTP registers and do internal power on action. Therefore, any initial settings (such as 3Ah,3Bh,etc.) by MIPI should be set after Sleep-Out command with minimum delay time 100ms.

Note 2: When RST keep low, MIPI lanes must go to LP00 state to avoid leakage current!! When RST goes to high, MIPI lanes must go to LP11 state.

#### Power Off Sequence

| VDDI                      |                                                                                   | 90%      |

|---------------------------|-----------------------------------------------------------------------------------|----------|

| AVDD                      | 1POFF2<br>1POFF2<br>1POFF1                                                        | 10%      |

| AVEE                      | 10%<br>50%<br>90%                                                                 |          |

| RST                       | VII                                                                               | \        |

| MIPI Video Strea          | n Packet                                                                          |          |

| Command Transf<br>< MIPI> | Backlight Control Setting Display-off + Sleep-in<br>command tSOFF2<br>LP-11 LP-00 |          |

| Backlight                 | tBLOFF tSLPIN                                                                     |          |

| PEC. NUMBER               | SPEC TITLE                                                                        | PAGE     |

| SXXX-XXXX                 | VS035ZSM-NW0-69P0 Product Specification                                           | 19 OF 34 |

|                           |                                                                                   |          |

B2006-5006-O (3/3)

P0

2017.03.20

| Item                                                         | Symbol  | Condition | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|---------|-----------|------|------|------|------|

| AVDD - AVEE delay time<br>(10% to 10%)                       | tPON1   | Power On  | 0    | -    | -    | us   |

| AVDD - AVEE delay time<br>(90% to 90%)                       | tPON2   | Power On  | 0    | -    | -    | us   |

| VDDI On to AVDD On time<br>(90% to 10%)                      | tsVSP   | Power On  | 1    | -    | -    | ms   |

| All Power On to RST Hi-level time<br>(90% to VIL)            | tRW     | Power On  | 10   | -    | -    | ms   |

| RST Hi-level (VIH) to 1st Command<br>time                    | tRT1    | Power On  | 10   | -    | -    | ms   |

| (MIPI goes to LP11 state) to<br>RST goes to High-level (VIL) | tRT2    | Power On  | 0    |      | -    | us   |

| SLPOUT Sequence Request time                                 | tSLPOUT | Power On  | 100  | -    | -    | ms   |

| Display On Command to BL On time                             | tBLON   | Power On  | 40   | -    | -    | ms   |

| AVDD - AVEE delay time<br>(10% to 10%)                       | tPOFF1  | Power Off | 0    | -    | -    | us   |

| AVDD - AVEE delay time<br>(90% to 90%)                       | tPOFF2  | Power Off | 0    | -    | -    | us   |

| AVDD Off to VDDI Off time<br>(10% to 90%)                    | thVSP   | Power Off | 0    | -    | -    | us   |

| RST Low to VDDI Off time<br>(VIH to 90%)                     | tROFF   | Power Off | 0    | -    | -    | us   |

| BL Off to Display Off Command time                           | tBLOFF  | Power Off | 0    | -    | -    | us   |

| SLPIN Sequence Request time                                  | tSLPIN  | Power Off | 60   | -    | -    | ms   |

| SLPIN Finished to<br>MIPI Video Stream Off                   | tSOFF1  | Power Off | 0    | -    | -    | us   |

| RST goes to Low-level (VIH) to<br>(MIPI goes to LP00 state)  | tSOFF2  | Power Off | 0    | -    | -    | us   |

About the "H" level and "L" level definition, please refer to the below table:

| Input / Output                               |        |         |      |         |      |  |

|----------------------------------------------|--------|---------|------|---------|------|--|

| Item                                         | Symbol | Min.    | Тур. | Max.    | Unit |  |

| Logic High level input voltage (Except RESX) | VIH    | 0.7VDDI | -    | VDDI    | V    |  |

| Logic Low level input voltage (Except RESX)  | VIL    | VSS     | -    | 0.3VDDI | V    |  |

| Logic High level input voltage (RESX)        | VIH    | 0.8VDDI | -    | VDDI    | V    |  |

| Logic Low level input voltage (RESX)         | VIL    | VSS     | -    | 0.2VDDI | V    |  |

| Logic High level input voltage (ENPWRP/N)    | VIH    | 0.7AVDD | -    | AVDD    | V    |  |

| Logic Low level input voltage (ENPWRP/N)     | VIL    | AVSS    | -    | 0.3AVDD | V    |  |

Note 1: VDDI=1.7 to 1.9V, AVDD=5.4 to 6.0V, AVEE=-6.0 to -5.4V, AVSS=VSS=0V, Ta=-40 ℃ to 70 ℃ (to +85 ℃ no damage)

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 20 OF 34 |

B2006-5006-O (3/3)

2017.03.20

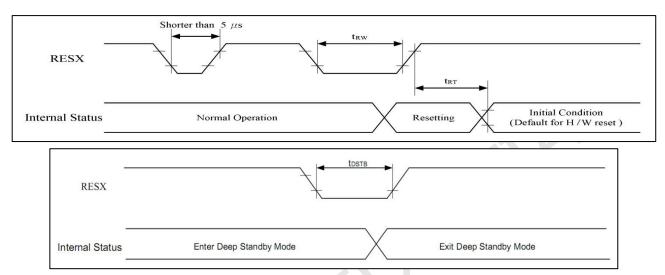

## 7.2 Reset Input Timing

#### (VSS=VSSI=DVSS=0V, VDDI=1.65V to 1.95V, VDDAM=1.65V to 1.95V)

| Signal | Symbol                    | Parameter                             | MIN | ТҮР | MAX | Unit |

|--------|---------------------------|---------------------------------------|-----|-----|-----|------|

|        | t <sub>RW</sub>           | Reset pulse duration (Note 1)         | 10  | -   | -   | ms   |

| RESX   | t Depart corneal (Nate 2) | -                                     | -   | 10  | ms  |      |

| RESA   | <sup>L</sup> RT           | t <sub>RT</sub> Reset cancel (Note 2) | -   | -   | 120 | ms   |

|        | t <sub>DSTB</sub>         | Reset pulse duration                  | 10  | -   | -   | ms   |

Note :

- The reset cancel also includes required time for loading ID bytes, VCOM setting and other settings from EEPROM (or similar device) to registers.

This loading is done every time when there is HW reset cancel time (tRT) within 10 ms after a rising edge of RESX.

Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below:

| RESX Pulse       | Action         |

|------------------|----------------|

| Shorter than 5µs | Reset Rejected |

- During the Resetting period, the display will be blanked(The display is entering blanking sequence, which maximum time is 120 ms, when Reset

Starts at Sleep-Out status. The display remains the blank state in Sleep-In mode). Then return to Default condition for Hardware Reset.

- Spike Rejection also applies during a valid reset pulse as shown below:

- When Reset applied during Sleep-In Mode.

- When Reset applied during Sleep-Out Mode.

- It is necessary to wait 10ms after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120 ms.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 21 OF 34 |

B2006-5006-O (3/3)

B2006-5006-O (3/3)

## 7.4 MIPI Interface Characteristics

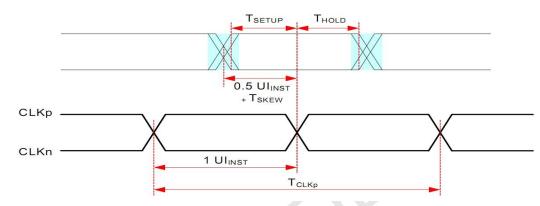

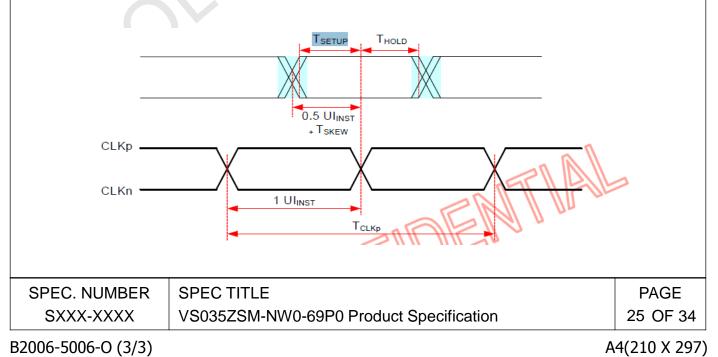

## High Speed Data Transmission: Data-Clock Timing

| Item                                               | Symbol                          | Min.  | Тур. | Max. | Unit               | Notes |

|----------------------------------------------------|---------------------------------|-------|------|------|--------------------|-------|

| UI instantaneous                                   | UI <sub>INST</sub>              | 1     |      | 4    | ns                 | 1,2,7 |

| Data to Clock Skew<br>[measured at tansmitter]     | T <sub>SKEW</sub> [TX]          | -0.15 |      | 0.15 | UI <sub>INST</sub> | 3     |

| Data to Clock Setup Time<br>[measured at receiver] | T <sub>SETUP</sub> [RX]         | 0.15  |      | 0.15 | UI <sub>INST</sub> | 4     |

| Data to Clock Hold Time<br>[measured at reciever]  | T <sub>HOLD</sub> [RX]          | 0.15  |      | 0.15 | UI <sub>INST</sub> | 4     |

|                                                    | . /.                            | 150   |      |      | ps                 | 6     |

| 20% - 80% rise time and fall time                  | t <sub>R</sub> / t <sub>F</sub> |       |      | 0.3  | UI <sub>INST</sub> | 5     |

Note :

- 1. This value corresponds to a minimum 250 Mbps data rate.

- 2. The minimum UI shall not be violated for any single bit period, i.e., any DDR half cycle within a data burst.

- 3. Total silicon and package delay budget of 0.3\* UIINST when D-PHY is supporting maximum data rate = 1Gbps.

- 4. Total setup and hole window for receiver of 0.3\* UIINST when D-PHY is supporting maximum data rate = 1Gbps.

- 5. Applicable when operating at HS bit rates  $\leq 1$  Gbps (UI  $\geq 1$  ns).

- 6. Applicable for all HS bit rates. However, to avoid excessive radiation, bit rates ≤1 Gbps (UI ≥1 ns), should not use values below 150 ps.

- 7. For MIPI speed limitation:

- [1] Per lane bandwidth is 1Gbps,

- [2] Total Bit Rate: 4Gbps for 8-8-8; 2.67 Gbps for 6-6-6; and for5-6-5.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 23 OF 34 |

B2006-5006-O (3/3)

2017.03.20

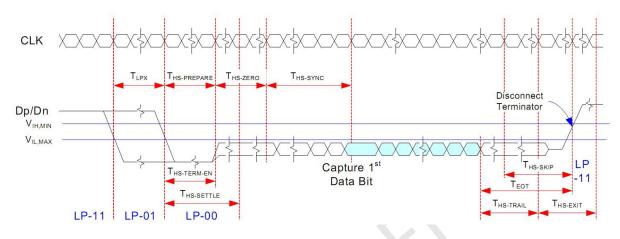

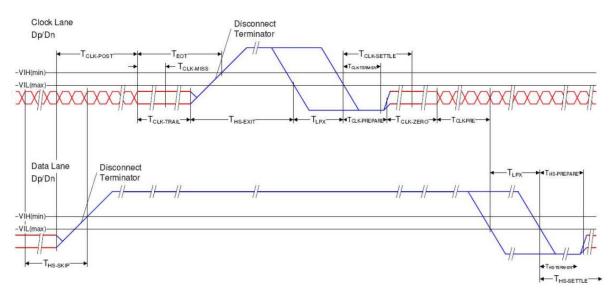

## High-Speed Data Transmission in Bursts

| Item                                                                                                  | Symbol                  | Min.    | Тур. | Max.         | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------------|---------|------|--------------|------|

| Time to drive LP-00 to prepare for HS transmission                                                    | T <sub>HS-PREPARE</sub> | 40+4UI  |      | 85+6UI       | ns   |

| Time from start of tHS-TRAIL or tCLK-TRAIL<br>period to start of LP-11 state                          | Τ <sub>ΕΟΤ</sub>        |         |      | 105+12<br>UI | ns   |

| Time to enable Data Lane receiver line<br>termination measured from when Dn<br>cross VIL,MAX          | T <sub>HS-TERM-EN</sub> |         |      | 35+4UI       | ns   |

| Time to drive flipped differential state after<br>last payload data bit of a HS<br>transmission burst | T <sub>HS-TRAIL</sub>   | 60+4UI  |      |              | ns   |

| Time-out at RX to ignore transition period of<br>EoT                                                  | T <sub>HS-SKIP</sub>    | 40      |      | 55+4UI       | ns   |

| Time to drive LP-11 after HS burst                                                                    | T <sub>HS-EXIT</sub>    | 100     |      |              | ns   |

| Length of any Low-Power state period                                                                  | T <sub>LPX</sub>        | 50      |      |              | ns   |

| Sync sequence period                                                                                  | T <sub>HS-SYNC</sub>    |         | 8UI  |              | ns   |

| Minimum lead HS-0 drive period before the<br>Sync sequence                                            | T <sub>HS-ZERO</sub>    | 105+6UI |      |              | ns   |

Note :

- 1. The minimum value depends on the bit rate. Implementations should ensure proper operation for all the supported bit rates.

- 2. UI means Unit Interval, equal to one half HS the clock period on the Clock Lane.

- 3. TLPX is an internal state machine timing reference. Externally measured values may differ slightly from the specified values due to asymmetrical rise and fall times.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 24 OF 34 |

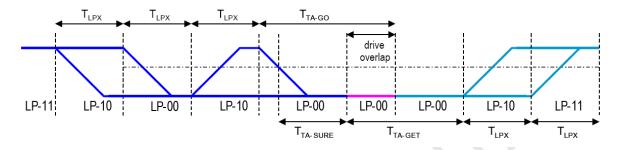

## **Turnaround Procedure**

| Item                                                               | Symbol                 | Min.             | Тур.              | Max.       | Unit |

|--------------------------------------------------------------------|------------------------|------------------|-------------------|------------|------|

| Length of any Low-Power state period :<br>Master side              | T <sub>LPX</sub>       | 50               |                   | 75         | ns   |

| Length of any Low-Power state period : Slave side                  | T <sub>LPX</sub>       | 50               |                   | 75         | ns   |

| Ratio of TLPX(MASTER)/TLPX(SLAVE)<br>between Master and Slave side | Ratio T <sub>LPX</sub> | 2/3              |                   | 3/2        |      |

| Time-out before new TX side start driving                          | T <sub>TA-SURE</sub>   | T <sub>LPX</sub> |                   | $2T_{LPX}$ | ns   |

| Time to drive LP-00 by new TX                                      | T <sub>TA-GET</sub>    |                  | 5T <sub>LPX</sub> |            | ns   |

| Time to drive LP-00 by new TX                                      | T <sub>TA-GO</sub>     |                  | 4T <sub>LPX</sub> |            | ns   |

# High Speed Data Transmission: Data-Clock Timing

P0

## Switching the Clock Lane between Clock Transmission and Low-Power Mode

| Item                                                                                                                             | Symbol                                                 | Min.          | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------|------|------|------|

| Time that the transmitter shall continue sending HS<br>clock after the last associated Data Lane has<br>transitioned to LP mode  | T <sub>CLK-POST</sub>                                  | 60ns+52<br>UI |      |      | ns   |

| Detection time that the clock has stopped toggling                                                                               | T <sub>CLK-MISS</sub>                                  |               |      | 60   | ns   |

| Time to drive LP-00 to prepare for HS clock<br>transmission                                                                      | T <sub>CLK-</sub><br>prepare                           | 38            |      | 95   | ns   |

| Minimum lead HS-0 drive period before starting<br>Clock                                                                          | T <sub>CLK-</sub><br>prepare<br>+T <sub>CLK-ZERO</sub> | 300           |      |      | ns   |

| Time to enable Clock Lane receiver line<br>termination measured from when Dn cross<br>VIL,MAX                                    | T <sub>HS-TERM-EN</sub>                                |               |      | 38   | ns   |

| Minimum time that the HS clock must be set prior<br>to any associated date lane beginning the<br>transmission from LP to HS mode | T <sub>CLK-PRE</sub>                                   | 8             |      |      | UI   |

| Time to drive HS differential state after last payload clock bit of a HS transmission burst                                      | T <sub>CLK-TRAIL</sub>                                 | 60            |      |      | ns   |

Note :

- 1. In one Port MIPI, the Tclk-post and Tclk-pre Spec is only define between the CLK lane and Data lanes of each port.

- In Two Port MIPI, the Tclk-post and Tclk-pre Spec is not only define between the DSl2A\_CLK lane and DSl2A\_Data lanes, but also define between the DSl2B\_CLK lane and DSl2A\_Data lanes. For DSl21\_CLK lane,DSl2B\_Data lanes and DSl2A\_Data lanes has the same rule.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 26 OF 34 |

B2006-5006-O (3/3)

2017.03.20

## 7.6 Initial Code Setting

## □ Speed & Porch Setting (for reference only)

|        | It         | tem                    | Symbol  | Min. | Тур. | Max. | Unit |

|--------|------------|------------------------|---------|------|------|------|------|

|        | Frame Rate |                        | -       | -    | 90   |      | Hz   |

|        |            | Line Time              | -       | -    | 3.2  | -    | us   |

| Speed* |            | Dot CLK                | -       | -    | TBD  | -    | MHz  |

|        |            | MIPI Speed             | -       | -    | TBD  | -    | Mbps |

|        |            | Horizontal total time  | Htotal  | -    | TBD  | -    | dot  |

| Horiz  |            | Horizontal Active time | Hactive |      | 1440 |      | dot  |

|        | Horizontal | Horizontal Pulse Width | Hsync   | -    | -    | -    | dot  |

|        |            | Horizontal Back Porch  | НВР     | -    | TBD  | 30   | dot  |

| Porch  |            | Horizontal Front Porch | HFP     | -    | TBD  | 50   | dot  |

| Porch  |            | Vertical Total         | Vtotal  | -    | TBD  | -    | line |

|        |            | Vertical Active        | Vactive |      | 1600 |      | line |

|        | Vertical   | Vertical Pulse Width   | Vsync   | -    | -    | -    | line |

|        |            | Vertical Back Porch    | VBP     | -    | TBD  | 10   | line |

|        | V          | Vertical Front Porch   | VFP     | -    | TBD  | 10   | line |

|        |            | Lane                   |         | -    | 4    | 8    | Lane |

\* The Driver IC supports VESA DSC V1.0 and V1.1 Data compression Decoder.

## □ Display Scan Direction

|           | Data  | a Direction | 36h         | HBP H Active A     | rea HFP      |

|-----------|-------|-------------|-------------|--------------------|--------------|

| 正向<br>扫描  |       | Driver 12   | 00h         | Active Area        | a            |

| 反向<br>扫描  |       | Dtiver K    | 03h         | VEP                |              |

| SPEC. NUM | 1BER  | SPEC TITLE  |             |                    | PAGE         |

| SXXX-XX   | XX    | VS035ZSM-N  | N0-69P0 Pro | duct Specification | 28 OF 34     |

|           | (2/2) |             |             |                    | A4(210 V 207 |

B2006-5006-O (3/3)

| ROF PRODUCT GROUP REV ISSU | JE DATE |

|----------------------------|---------|

| TFT LCD PRODUCT P0 201     | 7.03.20 |

# **8.0 MECHANICAL CHARACTERISTICS**

## 9.0 RELIABILITY TEST

The Reliability test items and its conditions are shown in below.

| <table 7.="" conditions="" reliability="" test=""></table> |

|------------------------------------------------------------|

|------------------------------------------------------------|

| No. | Test Items                                      | Conditions              |

|-----|-------------------------------------------------|-------------------------|

| 1   | High temperature storage                        | Ta = 70 °C, 48 hrs      |

| 2   | Low temperature storage                         | Ta = -40°C, 48 hrs      |

| 3   | High temperature & high humidity operation test | Ta = 55 ℃, 90%RH, 48hrs |

| 4   | High temperature operation                      | Ta = 55 ℃, 48 hrs       |

| 5   | Low temperature operation                       | Ta = -10 ℃, 48 hrs      |

Remark : The Reliability test items can only be applied to the BLU 10% on duty Mode

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 30 OF 34 |

B2006-5006-O (3/3)

P0

# **10.0 PACKING INFORMATION**

## **10.1 Packing Description**

| No. | Description               | Quantity | Size (mm) |

|-----|---------------------------|----------|-----------|

| 1   | LCM per Box               |          |           |

| 2   | LCM per Tray              |          |           |

| 3   | PET Tray                  |          |           |

| 4   | Antistatic Air Bubble Bag |          |           |

| 5   | Pulp Molding Pad          |          |           |

| 6   | Out Box                   |          |           |

| 7   | Belt tape                 |          |           |

| 8   | Distribution label        |          |           |

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 31 OF 34 |

B2006-5006-O (3/3)

| BOE                | PR        | ODUCT GROUP                    | REV | ISSUE DATE   |

|--------------------|-----------|--------------------------------|-----|--------------|

|                    | 7         | IFT LCD PRODUCT                | P0  | 2017.03.20   |

| 10.2 Packing Pro   | ocedure   |                                |     |              |

|                    |           |                                |     |              |

|                    |           |                                |     |              |

|                    | Step 1    | Step 2                         |     | Step 3       |

|                    |           |                                |     |              |

|                    |           |                                |     |              |

|                    | Step 4    | Step 5                         |     | Step 6       |

| 8                  |           |                                |     |              |

|                    |           |                                |     |              |

|                    |           |                                |     |              |

|                    | _         |                                |     |              |

|                    | Step 7    | Step8                          |     |              |

| SPEC. NUMBER       | SPEC TITL |                                |     | PAGE         |

| SXXX-XXXX          | VS035ZSN  | I-NW0-69P0 Product Specificati | on  | 32 OF 34     |

| B2006-5006-O (3/3) |           |                                |     | A4(210 X 297 |

| BOE            | PRODUCT GROUP   | REV | ISSUE DATE |

|----------------|-----------------|-----|------------|

| DOL            | TFT LCD PRODUCT | P0  | 2017.03.20 |

| 10.3 Box Label |                 |     |            |

| T.B.D.         |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

|                |                 |     |            |

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 33 OF 34 |

B2006-5006-O (3/3)

# **11.0 HANDLING & CAUTIONS**

- (1) Cautions when taking out the module

- Pick the pouch only, when taking out module from a shipping package.

- (2) Cautions for handling the module

- As the electrostatic discharges may break the LCD module, handle the LCD module with care. Peel a protection sheet off from the LCD panel surface as slowly as possible.

- As the LCD panel and back light element are made from fragile glass material, impulse and pressure to the LCD module should be avoided.

- As the surface of the polarizer is very soft and easily scratched, use a soft dry cloth without chemicals for cleaning.

- Do not pull the interface connector in or out while the LCD module is operating.

- Put the module display side down on a flat horizontal plane.

- Handle connectors and cables with care.

- (3) Cautions for the operation

- When the module is operating, do not lose Power, DSI signals. If any one of these signals is lost, the LCD panel would be damaged.

- Obey the supply voltage sequence. If wrong sequence is applied, the module would be damaged.

- (4) Cautions for the atmosphere

- Dew drop atmosphere should be avoided.

- Do not store and/or operate the LCD module in a high temperature and/or humidity atmosphere. Storage in an electro-conductive polymer packing pouch and under relatively low temperature atmosphere is recommended.

- (5) Cautions for the module characteristics

- Do not apply fixed pattern data signal to the LCD module at product aging.

- Applying fixed pattern for a long time may cause image sticking.

- (6) Other cautions

- Do not disassemble and/or re-assemble LCD module.

- Do not re-adjust variable resistor or switch etc.

- When returning the module for repair or etc., Please pack the module not to be broken.

- We recommend to use the original shipping packages.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS035ZSM-NW0-69P0 Product Specification | 34 OF 34 |